### **Question**

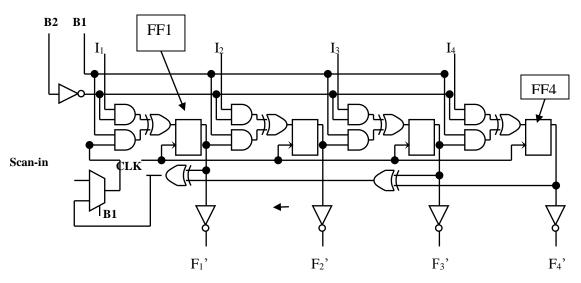

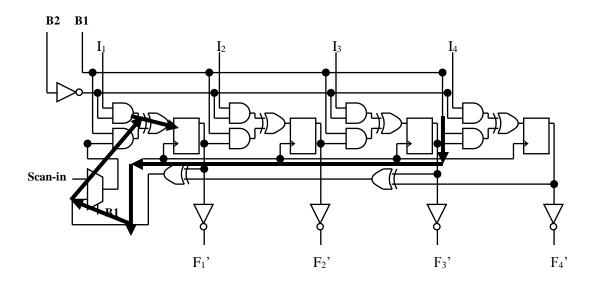

The circuit shown in Fig. 1 given below is a signature analyzer used for built in self test in digital systems. The timing characteristic of the gates and the flip-flops are listed below. The circuit operates at a supply voltage of  $5V\pm10\%$  in an ambient temperature range of 0 to 25 °C with a power dissipation 0f 1.5 W. The thermal resistance of the package is 40 °C/W and the process variation factor is  $\pm30\%$ . Determine:

a) The critical path in the circuit. What will be the typical delay of the path?

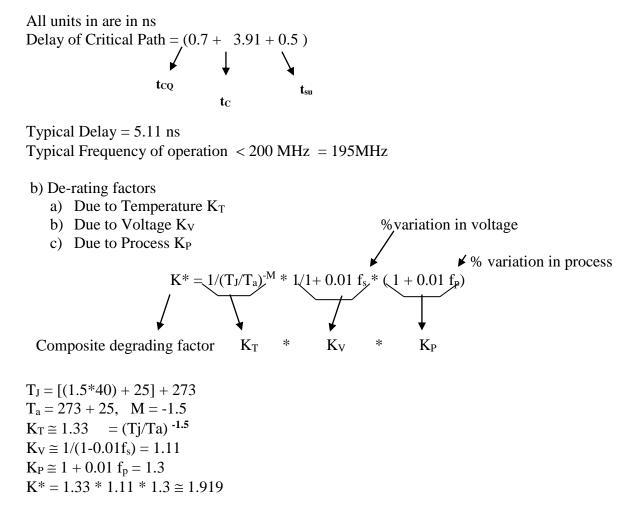

b) Maximum speed of operation for the worst conditions.

### Notes:

- 1. Arrival times of input signals B1, B2, Scan-in, is  $-\infty$

- 2. Signal  $I_1$  to  $I_4$  are registered inputs.

- 3. Temperature degrading factor M=1.5

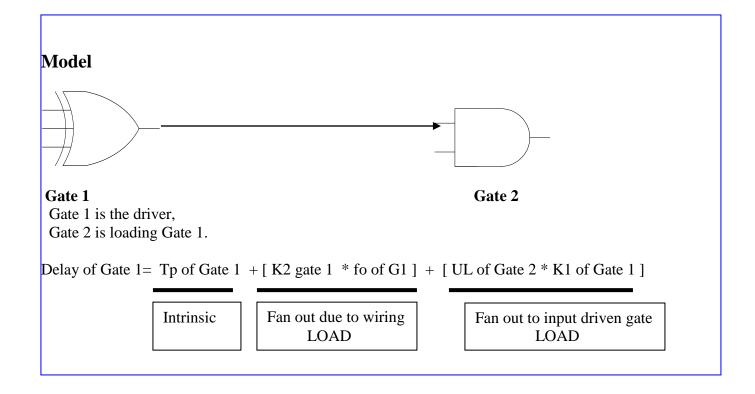

- 4. K1, K2 are input and output degrading factors.

| Component                | Tp (ns) | Input Loading (UL) | K1 (ns/UL) | K2 (ns/fo) |

|--------------------------|---------|--------------------|------------|------------|

| Inverter                 | 0.15    | 1                  | 0.08       | 0.1        |

| AND                      | 0.15    | 2                  | 0.08       | 0.1        |

| XOR                      | 0.3     | 2                  | 0.12       | 0.15       |

| 2:1 MUX                  | 0.4     | 1.5                | 0.12       | 0.15       |

| D-FF (tsu=0.5, th=0.2ns) | 0.7     | 2                  | 0.10       | 0.2        |

### **Solution**

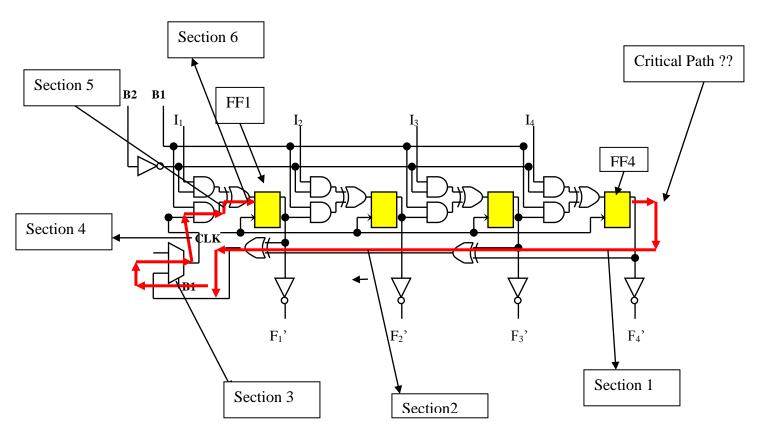

<u>Usually all paths have to be investigated</u>. In this case all paths in this circuit are almost of equal value except the feedback path(s). We will analyze only 2 paths for simplicity.

# <u>Part 1, Path 1</u>

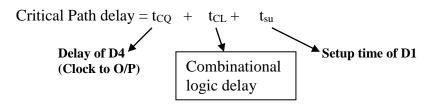

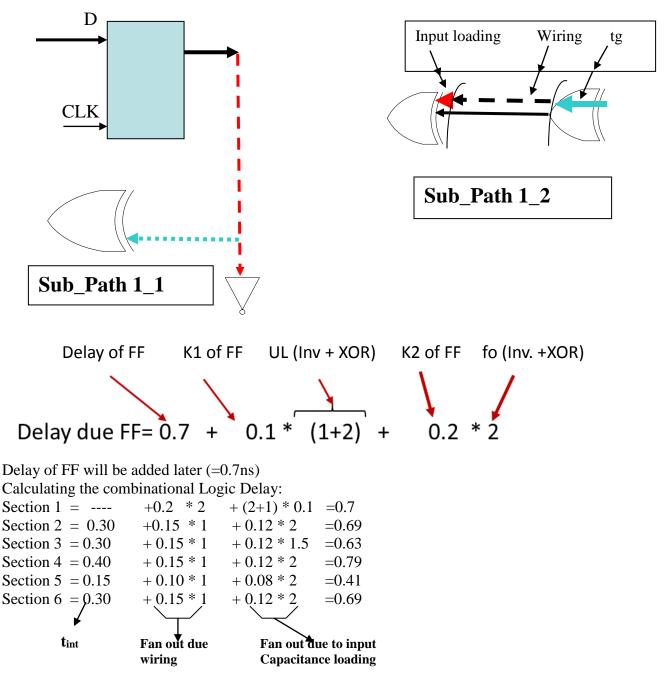

The selected path is the one outlined in heavy line, ie. the path from FF4 to FF1. Let us assume initially that the Critical Path of the circuit is from Flip-Flop 4 to Flip-Flop 1 We will use the following model to calculate delay of each individual component

$$\label{eq:tcl} \begin{split} t_{CL} &= Delay \ of \ combinational \ block, \ is \ made \ up \ of \ 6 \ sections \\ &= 3XOR_{delay} + MUX_{delay} + AND_{delay +} \ FF_{load} \end{split}$$

For example sub\_path1\_1 and sub\_path1\_2 calculation is shown below

$t_{CL}$  = Total of 6 sections =3.91ns

Maximum speed of operation is 195MHz/1.919 =101.6 ≅ 100 MHz

## Part 2, path 2

(This Section shows how a misdiagnosis of the critical path can affect operation of the circuit)

Now we check one more time more closely, and we see that there is another path that could have delay greater than the selected path.

This path has one extra fanout and AND gate loading on Reg. 3 than Reg. 4. Therefore the combinational logic part will be increased by 0.1 \* 2 + 0.2 \* 1 = 0.4 or total delay is 5.51ns giving a frequency of

Frequency = 181.4 MHz

When the derating factors are taken into account then the frequency of the operation is reduced further to: 181.4/1.99 = 91.2 MHz.

This example shows that even a little change in the loading of a path can affect the clock frequency a lot and renders our circuit incorrect.

### Question

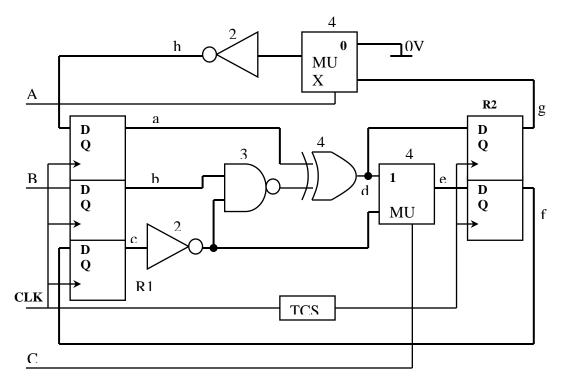

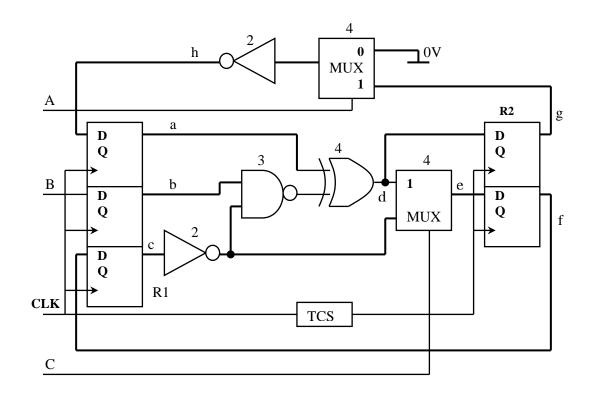

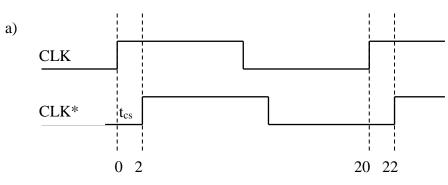

The circuit shown in the figure below has been initialized at  $t = -\infty$ . The arrival time of inputs A, B, and C is  $-\infty$  sec. The first active edge of the clock of R1 register arrive at t = 0 sec. The signal skew  $(t_{cs})$  in the clock path is 2 ns. Each F/F has:

Register switching time,  $t_{cq} = 6$  ns, set up time,  $t_{su} = 4$  ns, hold time,  $t_h = 2$  ns.

- a) Determine the arrival times, required times and the slack times for all nodes identified in the figure. Assume a clock rate of 50 MHz. Do you anticipate any timing problem?

- b) Determine the maximum speed of operation.

- c) What happens if the clock skew  $t_{cs} = -7$  ns.

### **Solution**

#### <u>a)</u>

For the arrival time start at the output of R1 reg. and follow the signal as it goes through the logic. For the required time start backward with the clock period, clock skew and the setup time to see when it is required to be stable at the input of the registers. For the feedback loops consider where the signal is feeding and when it has to be there. The table below is the results.

| Nodes | Arrival         | Requi | Slack                                     |    |   |

|-------|-----------------|-------|-------------------------------------------|----|---|

| a     | t <sub>cq</sub> | 6     | e-t <sub>mux-txor</sub>                   | 10 | 4 |

| b     | t <sub>cq</sub> | 6     | e-t <sub>mux</sub> -t <sub>AND-txor</sub> | 7  | 1 |

Violations

| с | t <sub>cq</sub>                      | 6   | e-t <sub>mux</sub> -t <sub>AND</sub> -t <sub>inv</sub> | _5   | * -1 | -1 |

|---|--------------------------------------|-----|--------------------------------------------------------|------|------|----|

| d | $t_{cq} + t_{xor}$                   | 10  | e- t <sub>mux</sub>                                    | 14 🗸 | *-1  |    |

|   | $t_{cq} + t_{xor} t_{AND}$           | 13  | T+t <sub>cs</sub> -t <sub>su</sub>                     |      |      |    |

|   | $t_{cq} + t_{xor} t_{AND} + t_{inv}$ | 15√ |                                                        |      |      |    |

| e | d + 4                                | 19  | T+t <sub>cs</sub> -t <sub>su</sub>                     | 18   | *-1  |    |

|   |                                      |     |                                                        |      |      |    |

| f | $t_{cq} + t_{cs}$                    | 8   | T-t <sub>su</sub>                                      | 16   | 8    |    |

| g | $t_{cq} + t_{cs}$                    | 8   | h-t <sub>inv</sub> -t <sub>mux</sub>                   | 10   | 2    |    |

| h | $t_{mux} + t_{inv}$                  | 6   | T-t <sub>su</sub>                                      | 16   | 2    |    |

|   | $g + t_{mux} + t_{inv}$              | 14  |                                                        |      |      |    |

There is a problem in <u>nodes "c" and "e" and "d" each have –1 slack time</u>. To overcome this problem, the circuit has to be redesigned or the clock frequency reduced.

b) The maximum speed then is  $T \ge 20 + (slack violation)$

$\begin{array}{ll} \mbox{or}\ T \geq t_{cq} + t_{CL^+}\ t_{su} - t_{cs} = 21 & T \geq 21 \\ f = 1/21 \ ns \cong 47.6 \ MHz \ or \ 45 \ Mhz. \ could \ be \ used \end{array}$

c) If the circuit has –ve clock skew, since the circuit has feedback then the negative clock skew will be helpful to the FB path but will be worse for the path where data and clock have the same direction. For proper operation then T has to be adjusted to

T =has to increase

$t_{cq} + t_{logic} + t_{su} + t_{cs} = 30 \text{ ns}$

<u>6+13+4+7</u> **Problem**

| Nodes | Arrival                                                                                                                   |                 | Requ                                                      | ired           | Slack |            |

|-------|---------------------------------------------------------------------------------------------------------------------------|-----------------|-----------------------------------------------------------|----------------|-------|------------|

| а     | t <sub>cq</sub>                                                                                                           | 6               | e-t <sub>mux-txor</sub>                                   | 10             | 4     |            |

| b     | t <sub>cq</sub>                                                                                                           | 6               | e-t <sub>mux</sub> -t <sub>AND-txor</sub>                 | 7              | 1     | Violetiona |

| с     | t <sub>cq</sub>                                                                                                           | 6               | e-t <sub>mux</sub> -t <sub>AND</sub> -t <sub>inv</sub>    | _5             | -1    | Violations |

| d     | $ \begin{array}{l} t_{cq} + t_{xor} \\ t_{cq} + t_{xor} \_ t_{AND} \\ t_{cq} + t_{xor} \_ t_{AND} + t_{inv} \end{array} $ | 10<br>13<br>15√ | e- t <sub>mux</sub><br>T+t <sub>cs</sub> -t <sub>su</sub> | $14 \sqrt{18}$ | *-1   |            |

| e     | d + 4                                                                                                                     | 19              | T+t <sub>cs</sub> -t <sub>su</sub>                        | 18             | *-1   | J¥         |

| f | $t_{cq} + t_{cs}$       | 8  | T-t <sub>su</sub>                    | 16 | 8 |

|---|-------------------------|----|--------------------------------------|----|---|

| g | $t_{cq} + t_{cs}$       | 8  | h-t <sub>inv</sub> -t <sub>mux</sub> | 10 | 2 |

| h | $t_{mux} + t_{inv}$     | 6  | T-t <sub>su</sub>                    | 16 | 2 |

|   | $g + t_{mux} + t_{inv}$ | 14 |                                      |    |   |