# FPGA *Express* VHDL Reference Manual

December 1997

Comments? E-mail your comments about Synopsys documentation to doc@synopsys.com

#### **Copyright Notice and Proprietary Information**

Copyright © 1997 Synopsys, Inc. All rights reserved. This software and documentation are owned by Synopsys, Inc., and furnished under a license agreement. The software and documentation may be used or copied only in accordance with the terms of the license agreement. No part of the software and documentation may be reproduced, transmitted, or translated, in any form or by any means, electronic, mechanical, manual, optical, or otherwise, without prior written permission of Synopsys, Inc., or as expressly provided by the license agreement.

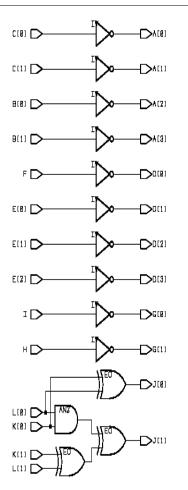

#### **Right to Copy Documentation**

The license agreement with Synopsys permits licensee to make copies of the documentation for its internal use only. Each copy shall include all copyrights, trademarks, service marks, and proprietary rights notices, if any. Licensee must assign sequential numbers to all copies. These copies shall contain the following legend on the cover page:

"This document is duplicated with the permission of Synopsys, Inc. for the exclusive use of \_\_\_\_\_\_ and its employees. This is copy number \_\_\_\_\_\_."

#### **Destination Control Statement**

All technical data contained in this publication is subject to the export control laws of the United States of America. Disclosure to nationals of other countries contrary to United States law is prohibited. It is the reader's responsibility to determine the applicable regulations and to comply with them.

#### Disclaimer

SYNOPSYS, INC., AND ITS LICENSORS MAKE NO WARRANTY OF ANY KIND, EXPRESS OR IMPLIED, WITH REGARD TO THIS MATERIAL, INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR A PARTICULAR PURPOSE.

#### Trademarks

#### Trademarks

- Synopsys, the Synopsys logo, BiNMOS-CBA, CMOS-CBA, COSSAP, DESIGN (ARROWS), DesignPower, DesignWare, dont\_use, ExpressModel, in-Sync, LM-1000, LM-1200, Logic Modeling, the Logic Modeling logo, Memory Architect, ModelAccess, ModelTools, PathMill, *PL*debug, SmartLicense, SmartLogic, SmartModel, SmartModels, SNUG, SOLV-IT!, SourceModel Library, Stream Driven Simulator, Synopsys VHDL Compiler, Synthetic Designs, Synthetic Libraries, TestBench Manager, and TimeMill are registered trademarks of Synopsys, Inc.

- 3-D Debugging, AMPS, Arcadia, Arkos, Behavioral Compiler, CBA Design System, CBA-Frame, characterize, Chip Architect, Compiled Designs, Core Network, Cyclone, Data Path Express, DataPath Architect, DC Expert, DC Expert Plus, DC Professional, DelayMill, Design Advisor, Core Store, Design Analyzer, Design Compiler, DesignSource, DesignTime, DesignWare Developer, Direct RTL, Direct Silicon Access, dont\_touch, dont\_touch\_network, ECL Compiler, ECO Compiler, Embedded System Prototype, Floorplan Manager, Formality, FoundryModel, FPGA Compiler, FPGA Express, Frame Compiler, Floorplan Manager, Formality, FoundryModel, FPGA Compiler, FPGA Express, Frame Compiler, Interactive Waveform Viewer, Library Compiler, LM-1400, LM-700, LM-family, Logic Model, ModelSource, ModelWare, Module Compiler, MS-3200, MS-3400, Power Compiler, PowerArc, PowerGate, PowerMill, PrimeTime, RailMill, RTL Analyzer,Shadow Debugger, Silicon Architects, SimuBus, SmartCircuit, SmartModel Windows, Source-Level Design, SourceModel, SWIFT, SWIFT Interface, Synopsys Graphical Environment, Test Compiler Plus, Test Compiler Plus, Test Manager, TestSim, Timing Annotator, Trace-On-Demand, VHDL System Simulator, Visualyze, Vivace, VSS Expert, and VSS Professional are trademarks of Synopsys, Inc.

All other products are trademarks of their respective holders and should be treated as such.

Printed in the U.S.A.

## **Table of Contents**

| 1 | Using FPGA Express with VHDL |                                             |  |  |

|---|------------------------------|---------------------------------------------|--|--|

|   |                              | Hardware Description Languages1             |  |  |

|   |                              | Typical Uses for HDLs                       |  |  |

|   |                              | Advantages of HDLs1-2                       |  |  |

|   |                              | About VHDL                                  |  |  |

|   |                              | FPGA Express Design Process                 |  |  |

|   |                              | Using FPGA Express to Compile a VHDL Design |  |  |

|   |                              | Design Methodology1-7                       |  |  |

| 2 | <b>Description Styles</b>    |                                             |  |  |

|   |                              | Design Hierarchy                            |  |  |

|   |                              | Data Types                                  |  |  |

|   |                              | Design Constraints                          |  |  |

|   |                              | Register Selection                          |  |  |

|   |                              | Asynchronous Designs                        |  |  |

|   |                              | Language Constructs                         |  |  |

| 3 | Describing Designs           |                                             |  |  |

|   |                              | VHDL Entities                               |  |  |

|   |                              | VHDL Constructs                             |  |  |

|   |                              | Entities                                    |  |  |

|   |                              |                                             |  |  |

iii

| Architectures                                  |      |

|------------------------------------------------|------|

| Configurations                                 |      |

| Processes                                      |      |

| Subprograms                                    |      |

| Packages                                       |      |

| Using a Package                                | 3-10 |

| Package Structure                              | 3-11 |

| Package Declarations                           | 3-11 |

| Package Bodies                                 | 3-12 |

| Defining Designs                               | 3-13 |

| Entity Specifications                          | 3-13 |

| Entity Generic Specifications                  | 3-14 |

| Entity Port Specifications                     | 3-14 |

| Entity Architectures.                          | 3-15 |

| Entity Configurations                          | 3-18 |

| Subprograms                                    | 3-19 |

| Subprogram Declarations                        |      |

| Subprogram Bodies                              |      |

| Subprogram Overloading                         |      |

| Operator Overloading.                          | 3-23 |

| Type Declarations                              |      |

| Subtype Declarations                           |      |

| Constant Declarations                          |      |

| Signal Declarations                            |      |

| Resolution Functions                           |      |

| Variable Declarations                          |      |

| Structural Design                              | 3-29 |

| Using Hardware Components                      | 3-30 |

| Component Declaration.                         |      |

| Sources of Components                          |      |

| Consistency of Component Ports                 |      |

| Component Instantiation Statement              |      |

| Mapping Generic Values                         |      |

| Mapping Port Connections                       |      |

| Technology-Independent Component Instantiation | 3-34 |

|                                                |      |

## 4 Data Types

| Enumeration Types           | 4-2 |

|-----------------------------|-----|

| Enumeration Overloading     | 4-3 |

| Enumeration Encoding        |     |

| Enumeration Encoding Values | 4-5 |

| Integer Types               | 4-6 |

| Array Types                 | 4-7 |

| Constrained Array           | 4-7 |

| Unconstrained Array         | 4-8 |

iv

| Array Attributes.          |      |

|----------------------------|------|

| Record Types               |      |

| Predefined VHDL Data Types | 4-11 |

| BOOLEAN Data Type          |      |

| BIT Data Type              |      |

| CHARACTER Data Type        |      |

| INTEGER Data Type          |      |

| NATURAL Data Type          |      |

| POSITIVE Data Type         |      |

| STRING Data Type           |      |

| BIT_VECTOR Data Type       |      |

| Unsupported Data Types     |      |

| Physical Types.            |      |

| Floating Point Types       |      |

| Access Types               |      |

| File Types                 |      |

| SYNOPSYS Data Types        | 4-15 |

| Subtypes                   |      |

|                            |      |

## 5 Expressions

| Operators                           |

|-------------------------------------|

| Logical Operators5-                 |

| Relational Operators                |

| Adding Operators5-                  |

| Unary (Sign) Operators              |

| Multiplying Operators5-             |

| Miscellaneous Arithmetic Operators  |

| Operands                            |

| Operand Bit Width                   |

| Computable Operands                 |

| Literals                            |

| Numeric Literals                    |

| Character Literals                  |

| Enumeration Literals                |

| String Literals                     |

| Identifiers                         |

| Indexed Names                       |

| Slice Names                         |

| Limitations on Null Slices          |

| Limitations on Noncomputable Slices |

| Records and Fields                  |

| Aggregates                          |

| Attributes                          |

| Function Calls                      |

| Qualified Expressions               |

v

| <b>T C</b> | •       |      |      | <b>5 0</b> 0 |

|------------|---------|------|------|--------------|

| I Whe Conv | ereione |      |      | 5_74         |

|            |         | <br> | <br> |              |

## 6 Sequential Statements

| Assignment Statements                                 | 6-2  |

|-------------------------------------------------------|------|

| Assignment Targets                                    | 6-3  |

| Simple Name Targets                                   | 6-3  |

| Indexed Name Targets                                  | 6-4  |

| Slice Targets                                         | 6-5  |

| Field Targets                                         | 6-6  |

| Aggregate Targets                                     | 6-7  |

| Variable Assignment Statement                         | 6-8  |

| Signal Assignment Statement.                          | 6-9  |

| Variable Assignment                                   | 6-9  |

| Signal Assignment.                                    | 6-9  |

| if Statements                                         | 6-10 |

| Evaluating condition                                  | 6-11 |

| Using the if Statement to Imply Registers and Latches | 6-12 |

| case Statement                                        | 6-12 |

| Using Different Expression Types                      | 6-13 |

| Invalid case Statements                               | 6-14 |

| loop Statements                                       | 6-15 |

| loop Statement.                                       | 6-16 |

| while loop Statement                                  | 6-17 |

| for loop Statement                                    | 6-17 |

| next Statements                                       | 6-20 |

| exit Statements                                       | 6-22 |

| Subprograms                                           | 6-23 |

| Subprogram Calls                                      |      |

| Procedure Calls                                       | 6-25 |

| Function Calls                                        | 6-27 |

| return Statements                                     | 6-28 |

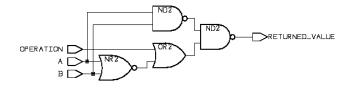

| Mapping Subprograms to Components (Entities)          | 6-29 |

| wait Statements                                       | 6-34 |

| Inferring Synchronous Logic                           |      |

| Combinational vs. Sequential Processes                |      |

| null Statements                                       | 6-40 |

## 7 Concurrent Statements

| process Statements            | 7-2 |

|-------------------------------|-----|

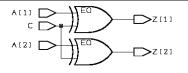

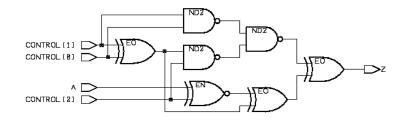

| Combinational Process Example | 7-3 |

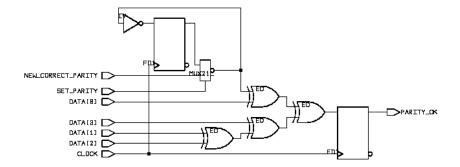

| Sequential Process Example    | 7-4 |

| Driving Signals               | 7-6 |

| block Statements              | 7-7 |

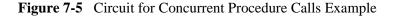

| Concurrent Procedure Calls    | 7-9 |

vi

| Concurrent Signal Assignments  | 7-11 |

|--------------------------------|------|

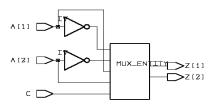

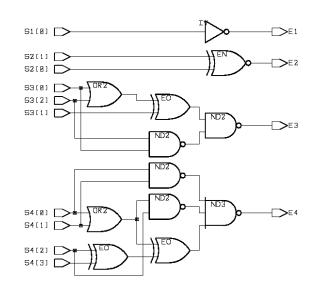

| Conditional Signal Assignment. | 7-12 |

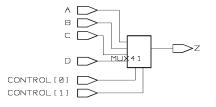

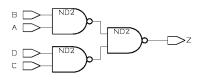

| Selected Signal Assignment     | 7-13 |

| Component Instantiations       | 7-15 |

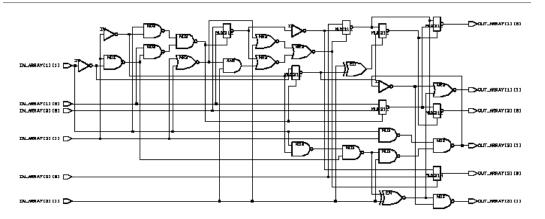

| generate Statements            | 7-17 |

| for generate Statement         | 7-17 |

| if generate Statement          | 7-20 |

|                                |      |

## 8 Register and Three-State Inference

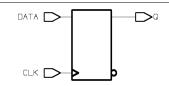

| Register Inference                                   | 8-1  |

|------------------------------------------------------|------|

| Using Register Inference                             | 8-2  |

| Describing Clocked Signals                           | 8-2  |

| wait versus if Statements                            | 8-4  |

| Recommended Use of Register Inference Capabilities   | 8-4  |

| Restrictions on Register Capabilities                | 8-6  |

| Delays in Registers                                  | 8-7  |

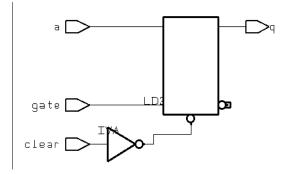

| Describing Latches                                   | 8-7  |

| Automatic Latch Inferencing                          | 8-8  |

| Restrictions on Latch Inference Capabilities         | 8-9  |

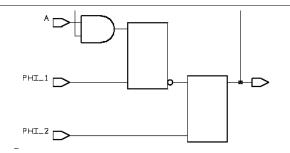

| Example—Design with Two-Phase Clocks                 | 8-10 |

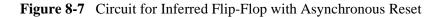

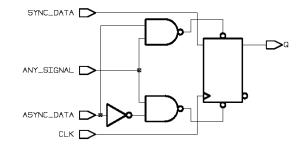

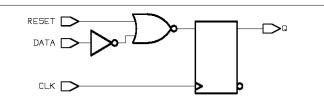

| Describing Flip-Flops                                | 8-11 |

| Flip-Flop with Asynchronous Reset.                   | 8-11 |

| Example—Synchronous Design with Asynchronous Reset . | 8-13 |

| Attributes                                           | 8-15 |

| async_set_reset                                      | 8-15 |

| Latch with Asynchronous Set or Clear Inputs          | 8-15 |

| sync_set_reset                                       | 8-16 |

| Flip-Flop with Synchronous Reset Input               |      |

| async_set_reset_local                                | 8-17 |

| sync_set_reset_local                                 | 8-19 |

| async_set_reset_local_all                            | 8-21 |

| sync_set_reset_local_all                             | 8-23 |

| one_hot                                              | 8-25 |

| one_cold                                             | 8-27 |

| FPGA Express Latch and Flip-Flop Inference           |      |

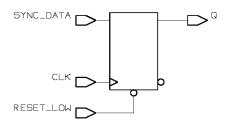

| Efficient Use of Registers                           | 8-30 |

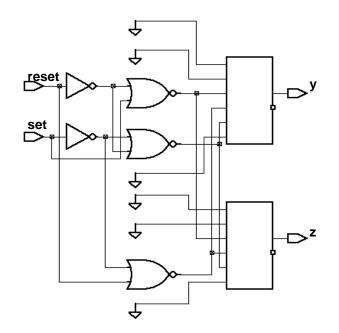

| Example—Using Synchronous and Asynchronous Processes | 8-32 |

| Three-State Inference                                |      |

| Assigning the Value Z.                               |      |

| Latched Three-State Variables                        | 8-37 |

|                                                      |      |

## 9 FPGA Express Directives

| Notation for FPGA Express Directives | 9-2 |

|--------------------------------------|-----|

| FPGA Express Directives.             | 9-2 |

| Translation Stop and Start Directives | 9-3 |

|---------------------------------------|-----|

| Resolution Function Directives        | 9-5 |

| Component Implication Directives      | 9-5 |

## 10 Synopsys Packages

| std_ | _logic_1164 Package          | <br> | <br>. 10-1 |

|------|------------------------------|------|------------|

| std_ | _logic_arith Package         | <br> | <br>. 10-2 |

| 1    | Using the Package            | <br> | <br>. 10-3 |

| I    | Modifying the Package        | <br> | <br>. 10-3 |

| ]    | Data Types                   | <br> | <br>. 10-4 |

|      | UNSIGNED                     | <br> | <br>. 10-5 |

|      | SIGNED                       | <br> | <br>. 10-5 |

| (    | Conversion Functions         | <br> | <br>. 10-6 |

| 1    | Arithmetic Functions         | <br> | <br>. 10-8 |

| (    | Comparison Functions         | <br> | <br>10-11  |

|      | Shift Functions              | <br> | <br>10-13  |

|      | Multiplication Using Shifts  | <br> | <br>10-14  |

| ]    | ENUM_ENCODING Attribute      | <br> | <br>10-14  |

| 1    | pragma built_in              | <br> | <br>10-15  |

|      | Two-Argument Logic Functions | <br> | <br>10-15  |

|      | One-Argument Logic Functions | <br> | <br>10-16  |

|      | Type Conversion              | <br> | <br>10-17  |

| t    | translate_off Directive      | <br> | <br>10-18  |

| std_ | _logic_misc Package          | <br> | <br>10-18  |

|      |                              |      |            |

## 11 VHDL Constructs

| VHDL Construct Support              |

|-------------------------------------|

| Design Units                        |

| Data Types                          |

| Declarations11-4                    |

| Specifications                      |

| Names                               |

| Operators                           |

| Operands and Expressions11-7        |

| Sequential Statements11-8           |

| Concurrent Statements11-9           |

| Predefined Language Environment11-9 |

| VHDL Reserved Words                 |

## Using FPGA Express with VHDL

FPGA *Express* translates and optimizes a VHDL description to an internal gate-level equivalent format. This format is then compiled for a given FPGA technology.

To work with VHDL, familiarize yourself with the following concepts:

- Hardware Description Languages

- About VHDL

- About FPGA Express

- Using FPGA Express

- A Model of the Design Process

The United States Department of Defense, as part of its Very-High-Speed Integrated Circuit (VHSIC) program, developed *VHSIC HDL* (VHDL) in 1982. VHDL describes the behavior, function, inputs, and outputs of a digital circuit design. VHDL is similar in style and syntax to modern programming languages, but includes many hardware-specific constructs.

FPGA *Express* reads and parses the supported VHDL syntax. Chapter 11, "HDL Constructs," lists all VHDL constructs and includes the level of Synopsys support provided for each construct.

## Hardware Description Languages

Hardware description languages (HDLs) are used to describe the architecture and behavior of discrete electronic systems.

HDLs were developed to deal with increasingly complex designs. An analogy is often made to the development of software description languages, from machine code (transistors and solder), to assembly language (netlists), to high-level languages (HDLs).

Top-down, HDL-based system design is most useful in large projects, where several designers or teams of designers are working concurrently. HDLs provide structured development. After major architectural decisions have been made, and major components and their connections have been identified, work can proceed independently on subprojects.

### **Typical Uses for HDLs**

HDLs typically support a mixed-level description, where structural or netlist constructs can be mixed with behavioral or algorithmic descriptions. With this mixed-level capability, you can describe system architectures at a high level of abstraction; then incrementally refine a design into a particular component-level or gate-level implementation. Alternatively, you can read an HDL design description into FPGA *Express*, then direct the compiler to synthesize a gate-level implementation automatically.

#### **Advantages of HDLs**

A design methodology that uses HDLs has several fundamental advantages over a traditional gate-level design methodology. Among the advantages are the following:

- You can verify design functionality early in the design process and immediately simulate a design written as an HDL description. Design simulation at this higher level, before implementation at the gate level, allows you to test architectural and design decisions.

- FPGA *Express* provides logic synthesis and optimization, so you can automatically convert a VHDL description to a gate-level implementation in a given technology. This methodology eliminates the former gate-level design bottleneck and reduces circuit design time and errors introduced when hand-translating a VHDL specification to gates. With FPGA *Express logic optimization*, you can automatically transform a synthesized design to

a smaller and faster circuit. You can apply information gained from the synthesized and optimized circuits back to the VHDL description, perhaps to fine-tune architectural decisions.

- HDL descriptions provide technology-independent documentation of a design and its functionality. An HDL description is more easily read and understood than a netlist or schematic description. Because the initial HDL design description is technology-independent, you can later reuse it to generate the design in a different technology, without having to translate from the original technology.

- VHDL, like most high-level software languages, provides strong *type checking*. A component that expects a four-bit-wide signal type cannot be connected to a three- or five-bit-wide signal; this mismatch causes an error when the HDL description is compiled. If a variable's range is defined as 1 to 15, an error results from assigning it a value of 0. Incorrect use of types has been shown to be a major source of errors in descriptions. Type checking catches this kind of error in the HDL description even before a design is generated.

## About VHDL

VHDL is one of a few HDLs in widespread use today. VHDL is recognized as a standard HDL by the Institute of Electrical and Electronics Engineers (IEEE Standard 1076, ratified in 1987) and by the United States Department of Defense (MIL-STD-454L).

VHDL divides *entities* (components, circuits, or systems) into an external or visible part (entity name and connections) and an internal or hidden part (entity algorithm and implementation). After you define the external interface to an entity, other entities can use that entity when they all are being developed. This concept of internal and external views is central to a VHDL view of system design. An entity is defined, relative to other entities, by its connections and behavior. You can explore alternate implementations (*architectures*) of an entity without changing the rest of the design.

After you define an entity for one design, you can reuse it in other designs as needed. You can develop libraries of entities for use by many designs or for a family of designs.

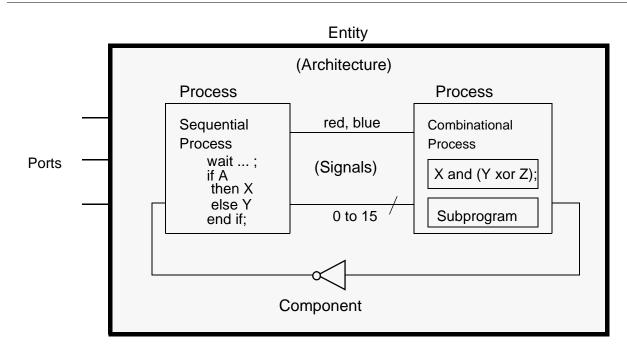

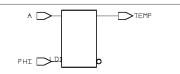

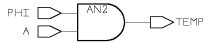

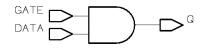

The VHDL hardware model is shown in Figure 1-1.

A VHDL *entity* (design) has one or more input, output, or inout *ports* that are connected (wired) to neighboring systems. An entity is composed of interconnected entities, *processes*, and *components*, all which operate concurrently. Each entity is defined by a particular *architecture*, which is composed of VHDL constructs such as arithmetic, signal assignment, or component instantiation statements.

In VHDL, independent *processes* model sequential (clocked) circuits, using flip-flops and latches, and combinational (unclocked) circuits, using only logic gates. Processes can define and call (*instantiate*) *subprograms* (subdesigns). Processes communicate with each other by *signals* (wires).

A signal has a source (driver), one or more destinations (receivers), and a user-defined *type*, such as "color" or "number between 0 and 15."

VHDL provides a broad set of constructs. With VHDL, you can describe discrete electronic systems of varying complexity (systems, boards, chips, or modules) with varying levels of abstraction.

VHDL language constructs are divided into three categories by their level of abstraction: *behavioral*, *dataflow*, and *structural*. These categories are described as follows:

#### behavioral

The functional or algorithmic aspects of a design, expressed in a sequential VHDL process.

#### dataflow

The view of data as flowing through a design, from input to output. An operation is defined in terms of a collection of data transformations, expressed as concurrent statements.

#### structural

The view closest to hardware; a model where the components of a design are interconnected. This view is expressed by component instantiations.

## FPGA Express Design Process

FPGA *Express* performs three functions:

- Translates VHDL to an internal format

- Optimizes the block-level representation through various optimization methods

- Maps the design's logical structure for a specific FPGA technology library

FPGA *Express* synthesizes VHDL descriptions according to the VHDL *synthesis policy* defined in Chapter 2, "Description Styles." The Synopsys VHDL synthesis policy has three parts: design methodology, design style, and language constructs. You use the VHDL synthesis policy to produce high quality VHDL-based designs.

## Using FPGA Express to Compile a VHDL Design

When a VHDL design is read into FPGA *Express*, it is converted to an internal database format so FPGA *Express* can synthesize and optimize the design. When FPGA *Express* optimizes a design, it can restructure part or all the design. You control the degree of restructuring. Options include:

- Fully preserving a design's hierarchy

- Allowing full modules to be moved up or down in the hierarchy

- Allowing certain modules to be combined with others

- Compressing the entire design into one module (called *flattening* the design) if it is beneficial

The following section describes the design process that uses FPGA *Express* with a VHDL simulator.

## **Design Methodology**

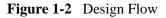

Figure 1-2 shows a typical design process that uses FPGA *Express* and a VHDL simulator.

These are the steps in Figure 1-2.

- Write a design description in VHDL. This description can be a combination of structural and functional elements (as shown in Chapter 2, "Description Styles"). This description is used with both FPGA *Express* and the Synopsys VHDL simulator.

- 2. Provide VHDL test drivers for the simulator. For information on writing

these drivers, see the appropriate simulator manual. The drivers supply test vectors for simulation and gather output data.

- 3. Simulate the design by using a VHDL simulator. Verify that the description is correct.

- 4. Use FPGA *Express* to synthesize and optimize the VHDL design description into a gate-level netlist. FPGA *Express* generates optimized netlists to satisfy timing constraints for a targeted FPGA architecture.

- 5. Use your FPGA development system to link the FPGA technology-specific version of the design to the VHDL simulator. The development system includes simulation models and interfaces required for the design flow.

- 6. Simulate the technology-specific version of the design with the VHDL simulator. You can use the original VHDL simulation drivers from Step 2 because module and port definitions are preserved through the translation and optimization processes.

- 7. Compare the output of the gate-level simulation (Step 6) against the output of the original VHDL description simulation (Step 3) to verify that the implementation is correct.

## **Description Styles**

2

The style of your initial VHDL description has a major effect on the characteristics of the resulting gate-level design synthesized by FPGA *Express*. The organization and style of a VHDL description determines the basic architecture of your design. Because FPGA *Express* automates most of the logic-level decisions required in your design, you can concentrate on architectural tradeoffs.

You can make some of the high-level architectural decisions that are needed by using FPGA *Express*. Certain VHDL constructs are well suited for synthesis. To make the decisions and use the constructs, you need to become familiar with the following concepts:

- · Design Hierarchy

- Data Types

- Design Constraints

- Register Selection

- Asynchronous Designs

- Language Constructs

## **Design Hierarchy**

FPGA *Express* maintains the hierarchical boundaries you define when using the structural view in VHDL. These boundaries have two major effects:

- 1. Each design entity specified in your VHDL description is synthesized separately and is maintained as a distinct design. The constraints for the design are maintained, and each design entity can be optimized separately in FPGA *Express*.

- 2. Component instantiations within VHDL descriptions are maintained during input. The instance name you give each user-defined entity is carried through to the gate-level implementation.

Chapter 3, "Describing Designs," discusses design entities, and Chapter 7, "Concurrent Statements," discusses component instantiations.

Note: FPGA Express does not automatically maintain or create a hierarchy of other nonstructural VHDL constructs such, as blocks, processes, loops, functions, and procedures. These elements of a VHDL description are translated in the context of their design. After reading in a VHDL design, you can group together the logic of a process, function, or procedure within the FPGA Express Implementation window.

The choice of hierarchical boundaries has a significant effect on the quality of the synthesized design. Using FPGA *Express*, you can optimize a design while preserving these hierarchical boundaries. However, FPGA *Express* only partially optimizes logic across hierarchical modules. Full optimization is possible across those parts of the design hierarchy that are collapsed in FPGA *Express*.

## **Data Types**

In VHDL, you must assign a data type to all ports, signals, and variables. The data type of an object defines the operations that can be applied to it. For example, the AND operator is defined for objects of type BIT, but not for objects of type INTEGER.

Data types are also important when your design is synthesized. The data type of an object determines its size (bit width) and its bit organization. The proper choice of data types greatly improves design quality and helps minimize errors.

See Chapter 4, "Data Types," for a discussion of VHDL data types.

## **Design Constraints**

You can describe the performance constraints for a design module within the FPGA *Express* Implementation window. Refer to the FPGA *Express* online help for further information.

### **Register Selection**

The placement of registers and the clocking scheme are important architectural decisions. There are two ways to define registers in your VHDL description. Each method has specific advantages:

- You can directly instantiate registers into a VHDL description, selecting from any element in your FPGA library. Clocking schemes can be arbitrarily complex. You can choose between a flip-flop and a latch-based architecture. The major disadvantages of this approach are

- The VHDL description is now specific to a given technology because you choose structural elements from that technology library. However, you can isolate this portion of your design as a separate entity, which you then connect to the remainder of the design.

- The description is more difficult to write.

- You can use the VHDL if and wait statements to direct FPGA *Express* to infer latches and flip-flops from the description. The advantages of this approach directly counter the disadvantages of the previous approach. When using register inference, the VHDL description is technology-independent and is much easier to write. This method allows FPGA *Express* to select the type of component inferred, on the basis of constraints. Therefore, if a specific component is necessary, instantiation should be used. Some types of registers and latches cannot be inferred.

See Chapter 8, "Register and Three-State Inference," for a discussion of register and latch inference.

## **Asynchronous Designs**

You can use FPGA *Express* to construct asynchronous designs with multiple clocks and gated clocks. However, although these designs are logically (statically) correct, they might not simulate or operate correctly, because of race conditions.

## Language Constructs

Another component of the VHDL synthesis policy is the set of VHDL constructs that describe your design, determine its architecture, and give consistently good results. The remainder of this manual discusses these constructs and their uses.

The concepts mentioned earlier in this chapter are described in the manual as follows:

#### Design Hierarchy

Chapter 3, "Describing Designs," describes the use and importance of hierarchy in VHDL designs. Chapter 7, "Concurrent Statements," explains how to instantiate (apply) existing components.

#### Data Types

Chapter 4, "Data Types," describes data types and their uses.

#### **Register Selection**

You can instantiate registers with the component instantiation statement discussed in Chapter 3, "Describing Designs," and Chapter 7, "Concurrent Statements." Chapter 6, "Sequential Statements," and Chapter 8, "Register and Three-State Inference," describe register inference with the VHDL if and wait statements.

## **Describing Designs**

To describe a design in VHDL, you need to be familiar with the following concepts:

- VHDL entities

- VHDL constructs

- Defining designs

- Structural designs

## **VHDL Entities**

Designs that are described with VHDL are composed of entities. An *entity* represents one level of the design hierarchy and can consist of a complete design, an existing hardware component, or a VHDL-defined object.

Each design has two parts: the entity specification and the architecture. The specification of an entity is its external interface. The architecture of an entity is its internal implementation. A design has only one entity specification (interface), but it can have multiple architectures (implementations). When an entity is compiled into a hardware design, a configuration specifies the architecture to use. An entity's specification and architecture can be contained in separate VHDL source files or in one VHDL source file.

Example 3-1 shows the entity specification of a simple logic gate (a 2-input NAND gate).

Example 3-1 VHDL Entity Specification

```

entity NAND2 is

port(A, B: in BIT; -- Two inputs, A and B

Z: out BIT); -- One output, Z = (A and B)'

end NAND2;

```

Note: In a VHDL description, a comment is prefixed by two hyphens (--). All characters from the hyphens to the end of the line are ignored by FPGA Express. The only exceptions to this rule are comments that begin with -- pragma or -- synopsys; these comments are FPGA Express directives.

After an entity statement declares an entity specification, that entity can be used by other entities in a design. The internal architecture of an entity determines its function.

Example 3-2, Example 3-3, and Example 3-4 show three different architectures for the entity NAND2. The three examples define equivalent implementations of NAND2. After optimization and synthesis, each implementation produces the same circuit, probably a 2-input NAND gate in the target technology. The architecture description style you use for this entity depends on your own preferences.

Example 3-2 shows how the entity NAND2 can be implemented with two components from a technology library. The entity inputs A and B are connected to AND gate U0, producing an intermediate signal I. Signal I is then connected to inverter U1, producing the entity output Z.

```

architecture STRUCTURAL of NAND2 is

signal I: BIT;

-- From a technology

component AND_2

library

port(I1, I2: in BIT;

O1: out BIT);

end component;

-- From a technology

component INVERT

library

port(I1: in BIT;

01: out BIT);

end component;

begin

U0: AND_2 port map (I1 => A, I2 => B, O1 => I);

U1: INVERT port map (I1 => I, O1 => Z);

end STRUCTURAL;

```

Example 3-3 shows how you can define the entity NAND2 by its logical function.

**Example 3-3** Dataflow Architecture for Entity NAND2

architecture DATAFLOW of NAND2 is begin Z <= A nand B; end DATAFLOW;

Example 3-4 shows another implementation of NAND2.

Example 3-4 RTL Architecture for Entity NAND2

```

architecture RTL of NAND2 is

begin

process(A, B)

begin

if (A = '1') and (B = '1') then

Z <= '0';

else

Z <= '1';

end if;

end process;

end RTL;

```

## **VHDL Constructs**

The top-level VHDL constructs work together to describe a design. The description consists of

#### Entities

The interfaces to other designs.

#### Architectures

The implementations of design entities. Architectures can specify connection through instantiation to other entities.

#### **Configurations**

The bindings of entities to architectures.

#### Processes

Collections of sequentially executed statements. Processes are declared within architectures.

#### Subprograms

Algorithms that can be used by more than one architecture.

#### Packages

Collections of declarations used by one or more designs.

#### Entities

A VHDL design consists of one or more entities. Entities have defined inputs and outputs, and perform a defined function. Each design has two parts: an entity specification and an architecture. The entity specification defines the design's inputs and outputs, and the architecture determines its function.

You can describe a VHDL design in one or more files. Each file contains entities, architectures, or packages. Packages define global information that can be used by several entities. You can often reuse VHDL design files in later design projects.

Figure 3-1 shows a block diagram of a VHDL design's hierarchical organization into files.

### Figure 3-1 Design Organization

| VHDL Design                                                                                             |                                         |  |  |  |  |  |  |

|---------------------------------------------------------------------------------------------------------|-----------------------------------------|--|--|--|--|--|--|

| VHDL Files                                                                                              |                                         |  |  |  |  |  |  |

| Packages                                                                                                |                                         |  |  |  |  |  |  |

| Declare constants, data types, components, and subprograms used by several designs or entities or both. |                                         |  |  |  |  |  |  |

| Entities                                                                                                | Architectures                           |  |  |  |  |  |  |

| Declare the interfaces to other entities and designs.                                                   | Define the implementations of entities. |  |  |  |  |  |  |

|                                                                                                         |                                         |  |  |  |  |  |  |

## Architectures

An architecture determines the function of an entity. Figure 3-2 shows the organization of an architecture. Not all architectures contain every construct shown.

| Declarations<br>Declare signals used to communicate be<br>and between concurrent statements and<br>types, constants, components, and subp | the interface ports. Declare |

|-------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|

| Concurrent Statements                                                                                                                     |                              |

| Blocks<br>Collect concurrent statements<br>together.                                                                                      | Component Instantiations     |

| Signal Assignments<br>Compute values and assign them to                                                                                   | Another entity.              |

| signals.                                                                                                                                  |                              |

An architecture consists of a declaration section where you declare signals, types, constants, components, and subprograms, followed by a collection of concurrent statements.

Signals connect the separate pieces of an architecture (the concurrent statements) to each other, and to the outside world, through interface ports. You declare each signal with a type that determines the kind of data it carries. Types, constants, components, and subprograms declared in an architecture are local to that architecture. To use these declarations in more than one entity or architecture, place them in a package, as described under "Packages" later in this chapter.

Each concurrent statement in an architecture defines a unit of computation that reads signals, performs a computation that is based on the signal values, and assigns computed values to signals. Concurrent statements compute all values simultaneously. Although the order of concurrent statements has no effect on execution order, the statements often coordinate their processing by communicating with each other through signals. The five kinds of concurrent statements are blocks, signal assignments, procedure calls, component instantiations, and processes. They are described as follows:

#### blocks

Group together a set of concurrent statements.

#### signal assignments

Assign computed values to signals or interface ports.

#### procedure calls

Call algorithms that compute and assign values to signals.

#### component instantiations

Create an instance of an entity, connecting its interface ports to signals or interface ports of the entity being defined. See "Structural Design" later in this chapter.

#### processes

Define sequential algorithms that read the values of signals, and compute new values to assign to other signals. Processes are discussed in the next section.

Concurrent statements are described in Chapter 7, "Concurrent Statements."

### Configurations

A configuration specifies one combination of an entity and its associated architecture.

Note: FPGA Express supports only configurations that associate one top-level entity with an architecture.

### Processes

Processes contain *sequential statements* that define algorithms. Unlike concurrent statements, sequential statements are executed in order. The order allows you to perform step-by-step computations. Processes read and write signals and interface port values to communicate with the rest of the architecture and with the enclosing system. Figure 3-3 shows the organization of constructs in a process. Processes need not use all the constructs listed.

Processes are unique in that they behave like concurrent statements to the rest of the design, but they are internally sequential. In addition, only processes can define variables to hold intermediate values in a sequence of computations.

Because the statements in a process are sequentially executed, several constructs are provided to control the order of execution, such as if and loop statements.

Chapter 6, "Sequential Statements," describes sequential statements.

| Process                                                                                                                                |                                                                  |

|----------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------|

| Declarations<br>Internal variables that hold temporary valu<br>of computations, as well as types, constan<br>subprograms used locally. |                                                                  |

| Sequential Statements                                                                                                                  |                                                                  |

| Signal Assignments<br><i>Compute values and assign them</i><br><i>to signals.</i>                                                      | loop Statements<br>Execute statements repeatedly.                |

| Procedure Calls<br>Invoke predefined algorithms.                                                                                       | next Statements<br>Skip remainder of a loop.                     |

| Variable Assignments<br>Store intermediate values<br>in variables.                                                                     | exit Statements<br>Terminate the execution<br>of a loop.         |

| if Statements<br>Conditionally execute groups of<br>sequential statements.                                                             | wait Statements<br><i>Wait for a clock signal.</i>               |

| case Statements<br>Select a group of sequential<br>statements to execute.                                                              | null Statements<br>Perform no action; these are<br>placeholders. |

### Subprograms

Subprograms, like processes, use sequential statements to define algorithms that compute values. Unlike processes, however, they cannot directly read or write signals from the rest of the architecture. All communication is through the subprogram's interface; each subprogram call has its own set of interface signals.

The two types of subprograms are functions and procedures. A function returns a single value directly. A procedure returns zero or more values through its interface. Subprograms are useful because you can use them to perform repeated calculations, often in different parts of an architecture.

Chapter 6, "Sequential Statements," describes subprograms.

#### Packages

You can collect constants, data types, component declarations, and subprograms into a VHDL package that can then be used by more than one design or entity. Figure 3-4 shows the typical organization of a package.

| Package                       |                             |

|-------------------------------|-----------------------------|

| Constant Declarations         | Type Declarations           |

| Define constant values used   | Declare the data types used |

| by designs.                   | by designs.                 |

| Component Declarations        | Subprograms                 |

| Declare interfaces for design | Declare algorithms used by  |

| entities.                     | designs.                    |

A package must contain at least one of the constructs listed in Figure 3-4.

- Constants in packages often declare system-wide parameters, such as data-path widths.

- VHDL data type declarations are often included in a package to define data types used throughout a design. All entities in a design must use common interface types; for example, common address bus types.

- Component declarations specify the interfaces to entities that can be instantiated in the design.

- Subprograms define algorithms that can be called anywhere in a design.

Packages are often sufficiently general so that you can use them in many different designs. For example, the std\_logic\_1164 package defines data types std\_logic and std\_logic\_vector.

#### Using a Package

The use statement allows an entity to use the declarations in a package. The supported syntax of the use statement is

use LIBRARY\_NAME.PACKAGE\_NAME.ALL;

LIBRARY\_NAME is the name of a VHDL library, and PACKAGE\_NAME is the name of the included package. A use statement is usually the first statement in a package or entity specification source file. Synopsys does not support different packages with the same name when they exist in different libraries. No two packages can have the same name.

#### Package Structure

Packages have two parts, the *declaration* and the *body*:

#### package declaration

Holds *public* information, including constant, type, and subprogram declarations.

#### package body

Holds *private* information, including local types and subprogram implementations (bodies).

Note: When a package declaration contains subprogram declarations, a corresponding package body must define the subprogram bodies.

#### **Package Declarations**

Package declarations collect information needed by one or more entities in a design. This information includes data type declarations, signal declarations, subprogram declarations, and component declarations.

#### Note: Signals declared in packages cannot be shared across entities. If two entities both use a signal from a given package, each entity has its own copy of that signal.

Although you can declare all this information explicitly in each design entity or architecture in a system, it is often easier to declare system information in a separate package. Each design entity in the system can then use the system's package.

The syntax of a package declaration is

```

package package_name is

{ package_declarative_item }

end [ package_name ];

```

where package\_name is the name of this package.

A package\_declarative\_item is any of these:

- use clause (to include other packages)

- Type declaration

- Subtype declaration

- Constant declaration

- Signal declaration

- Subprogram declaration

- Component declaration

Example 3-5 shows some package declarations.

**Example 3-5** Sample Package Declarations

package EXAMPLE is type BYTE is range 0 to 255; subtype NIBBLE is BYTE range 0 to 15; constant BYTE\_FF: BYTE := 255; signal ADDEND: NIBBLE; component BYTE\_ADDER port(A, B: in BYTE; C: out BYTE; OVERFLOW: out BOOLEAN); end component; function MY\_FUNCTION (A: in BYTE) return BYTE; end EXAMPLE; To use the example declarations above, add a use statement at the beginning of your design description as follows:

use WORK.EXAMPLE.ALL; entity . . . architecture . . .

#### **Package Bodies**

Package bodies contain the implementations of subprograms listed in the package declaration. However, this information is never seen by designs or entities that use the package. Package bodies can include the implementations (bodies) of subprograms declared in the package declaration and in internal support subprograms.

The syntax of a package body is

package body package\_name is

{ package\_body\_declarative\_item }

end [ package\_name ] ;

where package\_name is the name of the associated package.

A package\_body\_declarative\_item is any of these:

- use clause

- Subprogram declaration

- Subprogram body

- Type declaration

- Subtype declaration

- Constant declaration

For an example of a package declaration and body, see the std\_logic\_arith package supplied with FPGA *Express*.

## **Defining Designs**

The high-level constructs discussed earlier in this chapter involve

- Entity specifications (interfaces)

- Entity architectures (implementations)

- Subprograms

### **Entity Specifications**

An *entity specification* defines the characteristics of an entity that must be known before that entity can be connected to other entities and components.

For example, before you can connect a counter to other entities, you must specify the number and types of its inputs and outputs. The entity specification defines the ports (inputs and outputs) of an entity.

The syntax of an entity specification is

```

entity entity_name is

[ generic( generic_declarations) ; ]

[ port( port_declarations) ; ]

end [ entity_name ] ;

```

entity\_name is the name of the entity, generic\_declarations determine local constants used for sizing or timing the entity, and port\_declarations determine the number and type of inputs and outputs. Other declarations are not supported in the entity specification.

#### **Entity Generic Specifications**

Generic specifications are entity parameters. Generics can specify the bit widths of components (such as adders) or provide internal timing values.

A generic can have a default value. A generic is assigned a nondefault value only when the entity is instantiated (see "Component Instantiation Statement" later in this chapter) or configured (see "Entity Configurations," later in this chapter). Inside an entity, a generic is a constant value.

The syntax of generic\_declarations is

```

generic(

[ constant_name : type [ := value ]

{ ; constant_name : type [ := value ] }

);

```

constant\_name is the name of a generic constant, type is a previously defined data type, and the optional value is the default value of constant\_name.

Note: FPGA Express supports only INTEGER type generics.

#### **Entity Port Specifications**

The syntax of port\_declarations is

```

port(

[ port_name : mode port_type

{ ; port_name : mode port_type}]

);

```

port\_name is the name of a port; mode is either in, out, inout, or buffer; and port\_type is a previously defined data type.

The four port modes are

#### in

Can only be read.

#### out

Can only be assigned a value.

#### inout

Can be read and assigned a value. The value read is that of the port's incoming value, not the assigned value (if any).

#### buffer

Similar to out, but can be read. The value read is the assigned value. It can have only one driver. For more information on drivers, see "Driving Signals" in Chapter 7, "Concurrent Statements."

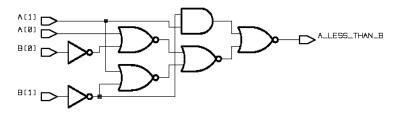

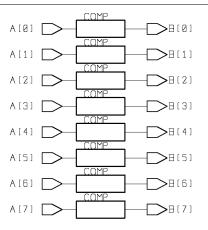

Example 3-6 shows an entity specification for a 2-input N-bit comparator, with a default bit width of 8.

Example 3-6 Interface for an N-Bit Counter

```

-- Define an entity (design) called COMP

-- that has 2 N-bit inputs and one output.

entity COMP is

generic(N: INTEGER := 8); -- default is 8 bits

port(X, Y: in BIT_VECTOR(0 to N-1);

EQUAL: out BOOLEAN);

end COMP;

```

#### **Entity Architectures**

Each entity architecture defines one implementation of the entity's function. An architecture can range in abstraction from an algorithm (a set of sequential statements within a process) to a structural netlist (a set of component instantiations).

The syntax of an architecture is

```

architecture architecture_name of entity_name is

{ block_declarative_item }

begin

{ concurrent_statement }

end [ architecture_name ] ;

```

architecture\_name is the name of the architecture, and entity\_name is the name of the entity being implemented.

A block\_declarative\_item is any of these:

- use clause

- Subprogram declaration

- Subprogram body

- Type declaration

- Subtype declaration

- Constant declaration

- · Signal declaration

- Component declaration

Concurrent statements are described in Chapter 7, "Concurrent Statements."

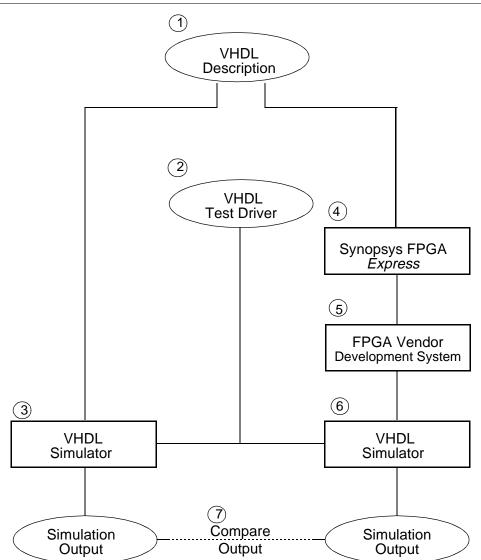

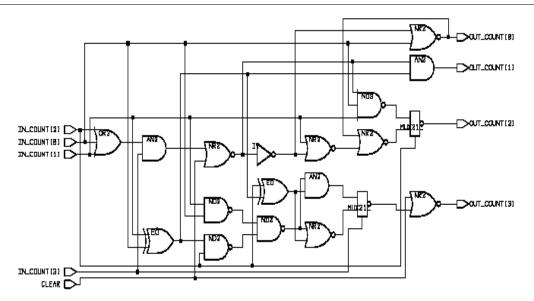

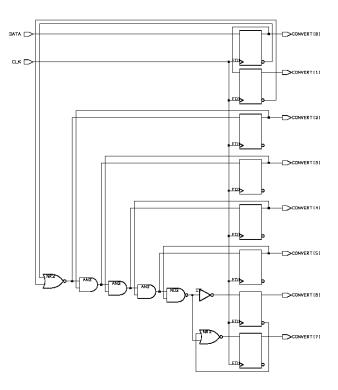

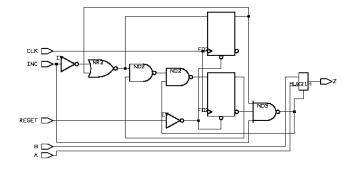

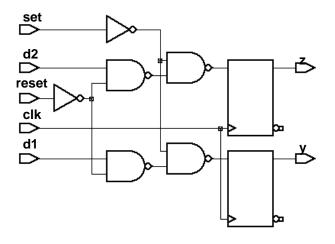

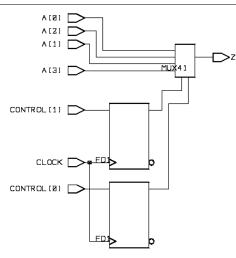

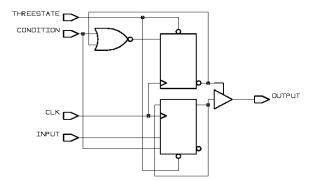

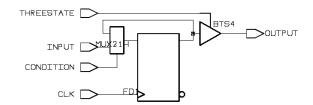

Example 3-7 shows a complete circuit description for a three-bit counter, entity specification (COUNTER3), and an architecture (MY\_ARCH). This example also includes a schematic of the resulting synthesized circuit.

```

Example 3-7 An Implementation of a Three-Bit Counter

```

```

entity COUNTER3 is

port ( CLK : in bit;

RESET: in bit;

COUNT: out integer range 0 to 7);

end COUNTER3;

architecture MY ARCH of COUNTER3 is

signal COUNT_tmp : integer range 0 to 7;

begin

process

begin

wait until (CLK'event and CLK = '1');

-- wait for the clock

if RESET = '1' or COUNT_tmp = 7 then

-- Ck. for RESET or max. count

COUNT_tmp <= 0;

else COUNT_tmp <= COUNT_tmp + 1;</pre>

-- Keep counting

end if;

end process;

COUNT <= COUNT_tmp;

end MY_ARCH;

```

Note: In an architecture, you must not declare constants or signals with the same name as any of the entity's ports. If you declare a constant or signal with a port's name, the new declaration hides that port name. If the new declaration is included in the architecture declaration (as shown in Example 3-8) and not in an inner block, FPGA Express reports an error.

```

entity X is

port(SIG, CONST: in BIT;

OUT1, OUT2: out BIT);

end X;

architecture EXAMPLE of X is

signal SIG : BIT;

constant CONST: BIT := '1';

begin

. . .

end EXAMPLE;

The error messages generated for Example 3-8 are:

SIG : BIT;

signal

~

Error: (VHDL-1872) line 13

Illegal redeclaration of SIG.

constant CONST: BIT := '1';

Error: (VHDL-1872) line 14

Illegal redeclaration of CONST.

```

### **Entity Configurations**

A configuration defines one combination of an entity and architecture for a design.

Note: FPGA Express supports only configurations that associate one top-level entity with an architecture.

The supported syntax for a configuration is

configuration configuration\_name of entity\_name is

for architecture\_name

end for;

end [ configuration\_name ];

configuration\_name is the name of this configuration, entity\_name is the name of a top-level entity, and architecture\_name is the name of the architecture to use for entity\_name.

Example 3-9 shows a configuration for the three-bit counter in Example 3-7. This configuration associates the counter's entity specification (COUNTER3) with an architecture (MY\_ARCH).

configuration MY\_CONFIG of COUNTER3 is

for MY\_ARCH

end for;

end MY\_CONFIG;

Note: If you do not specify a configuration for an entity with multiple architectures, IEEE VHDL specifies that the last architecture read is used. This is determined from the .mra (most recently analyzed) file.

### Subprograms

Subprograms describe algorithms that are meant to be used more than once in a design. Unlike component instantiation statements, when a subprogram is used by an entity or another subprogram, a new level of design hierarchy is not automatically created. However, you can manually define a subprogram as a new level of design hierarchy in the FPGA *Express* Implementation window.

Two types of subprograms, procedures and functions, can contain zero or more parameters:

### procedures

Procedures have no return value, but can return information to their callers by changing the values of their parameters.

### functions

A function has a single value that it returns to the caller, but it cannot change the value of its parameters.

Like an entity, a subprogram has two parts—its declaration and its body:

### declaration

Declares the interface to a subprogram: its name, its parameters, and its return value (if any).

### body

Defines an algorithm that gives the subprogram's expected results.

When you declare a subprogram in a package, the subprogram declaration must be in the package declaration, and the subprogram body must be in the package body. A subprogram defined inside an architecture has a body, but does not have a corresponding subprogram declaration.

### **Subprogram Declarations**

A subprogram declaration lists the names and types of its parameters and for functions, the type of its return value.

The syntax of a procedure declaration is

```

procedure proc_name [ ( parameter_declarations ) ] ;

```

proc\_name is the name of the procedure.

The syntax of a function declaration is

```

function func_name [ ( parameter_declarations ) ]

return type_name ;

```

func\_name is the name of the function, and type\_name is the type of the function's returned value.

The syntax of parameter\_declarations is the same as the syntax of port\_declarations:

```

[ parameter_name : mode parameter_type

{ ; parameter_name : mode parameter_type}]

```

parameter\_name is the name of a parameter; mode is either in, out, inout, or buffer; and parameter\_type is a previously defined data type.

Procedure parameters can use any mode. Function parameters must use only mode in. Signal parameters of type range cannot be passed to a subprogram.

Example 3-10 shows sample subprogram declarations for a function and a procedure.

Example 3-10 Two Subprogram Declarations

Note: When you call a subprogram, actual parameters are substituted for the declared formal parameters. Actual parameters are either constant values or signal, variable, constant, or port names. An actual parameter must support the formal parameter's type and mode. For example, an input port cannot be used as an out actual parameter, and a constant can be used only as an in actual parameter.

Example 3-11 shows some calls to the subprogram declarations from Example 3-10.

Example 3-11 Two Subprogram Calls

```

signal INT : INTEGER;

variable EVEN : BOOLEAN;

. . .

INT <= 7;

EVEN := IS_EVEN(INT);

. . .

variable TOP, BOT: NIBBLE;

. . .

BYTE_TO_NIBBLES("00101101", TOP, BOT);

```

### Subprogram Bodies

A subprogram body defines an implementation of a subprogram's algorithm.

The syntax of a procedure body is

```

procedure procedure_name [ (parameter_declarations)

] is

{ subprogram_declarative_item }

begin

{ sequential_statement }

end [ procedure_name ] ;

```

The syntax of a function body is

```

function function_name [ (parameter_declarations) ]

return type_name is

{ subprogram_declarative_item }

begin

{ sequential_statement }

end [ function_name ] ;

```

A subprogram\_declarative\_item is any of these:

- use clause

- Type declaration

- Subtype declaration

- · Constant declaration

- Variable declaration

- Attribute declaration

- Attribute specification

- Subprogram declaration (for local, or nested, subprograms)

- Subprogram body

Example 3-12 shows subprogram bodies for the sample subprogram declarations in Example 3-10.

Example 3-12 Two Subprogram Bodies

### Subprogram Overloading

You can overload subprograms; more than one subprogram can have the same name. Each subprogram that uses a given name must have a different parameter profile.

A parameter profile specifies a subprogram's number and type of parameters. This information determines which subprogram is called when more than one subprogram has the same name. Overloaded functions are also distinguished by the type of their return values.

Example 3-13 shows two subprograms with the same name, but different parameter profiles.

type SMALL is range 0 to 100; type LARGE is range 0 to 10000; function IS\_ODD(NUM: SMALL) return BOOLEAN; function IS\_ODD(NUM: LARGE) return BOOLEAN; signal A\_NUMBER: SMALL; signal B: BOOLEAN; ... B <= IS\_ODD(A\_NUMBER); -- Will call the first -- function above

### **Operator Overloading**

Predefined operators such as +, and, and mod can also be overloaded. By using overloading, you can adapt predefined operators to work with your own data types.

For example, you can declare new logic types, rather than use the predefined types BIT and INTEGER. However, you cannot use predefined operators with these new types unless you declare overloaded operators for the new logic type.

Example 3-14 shows how some predefined operators are overloaded for a new logic type.

Example 3-14 Operator Overloading

type NEW\_BIT is ('0', '1', 'X'); -- New logic type function "and"(I1, I2: in NEW\_BIT) return NEW\_BIT; function "or" (I1, I2: in NEW\_BIT) return NEW\_BIT; -- Declare overloaded operators for new logic type . . . signal A, B, C: NEW\_BIT; . . . C <= (A and B) or C;</pre>

VHDL requires overloaded operator declarations to enclose the operator name or symbol in double quotation marks, because they are infix operators (they are used between operands). If you declared the overloaded operators without quotation marks, a VHDL tool considers them functions rather than operators.

## **Type Declarations**

Type declarations define the name and characteristics of a type. Types and type declarations are fully described in Chapter 4, "Data Types." A type is a named set of values, such as the set of integers, or the set (red, green, blue). An object of a given type, such as a signal, can have any value of that type.

Example 3-14 shows a type declaration for type NEW\_BIT, and some functions and variables of that type.

Type declarations are allowed in architectures, packages, entities, blocks, processes, and subprograms.

### **Subtype Declarations**

Use subtype declarations to define the name and characteristics of a constrained subset of another type or subtype. A subtype is fully compatible with its parent type, but only over the subtype's range. Subtype declarations are described in Chapter 4, "Data Types."

The following subtype declaration (NEW\_LOGIC) is a subrange of the type declaration in Example 3-14.

subtype NEW\_LOGIC is NEW\_BIT range '0' to '1';

Subtype declarations are allowed wherever type declarations are allowed: in architectures, packages, entities, blocks, processes, and subprograms.

## Constant Declarations

Constant declarations create named values of a given type. The value of a constant can be read but not changed.

Constant declarations are allowed in architectures, packages, entities, blocks, processes, and subprograms.

Example 3-15 shows some constant declarations.

**Example 3-15** Constant Declarations

constant WIDTH: INTEGER := 8; constant X : NEW\_BIT := 'X'; You can use constants in expressions, as described in Chapter 5, "Expressions," and as source values in assignment statements, as described in Chapter 6, "Sequential Statements."

### Signal Declarations

Signal declarations create new named signals (wires) of a given type. Signals can be given default (initial) values. However, these initial values are not used for synthesis.

Signals with multiple drivers (signals driven by wired logic) can have associated resolution functions, as described in the next section.

Example 3-16 shows two signal declarations.

Example 3-16 Signal Declarations

signal A, B: BIT; signal INIT: INTEGER := -1;

Note: Ports are also signals, with the restriction that out ports cannot be read, and in ports cannot be assigned a value. You create signals either by port declarations or by signal declarations. You create ports only by port declarations.

You can declare signals in architectures, entities, and blocks, and use them in processes and subprograms. Processes and subprograms cannot declare signals for internal use.

You can use signals in expressions, as described in Chapter 5, "Expressions." Signals are assigned values by signal assignment statements, as described in Chapter 6, "Sequential Statements."

## **Resolution Functions**

Resolution functions are used with signals that can be connected (wired together). For example, if two drivers are directly connected to a signal, the resolution function determines whether the signal value is the AND, OR, or three-state function of the driving values.

Use resolution functions to assign the driving value when there are multiple drivers. For simulation, you can write an arbitrary function to resolve bus conflicts.

Note: A resolution function might change the value of a resolved signal, even if all drivers have the same value.

The resolution function for a signal is part of that signal's subtype declaration. You create a resolved signal in four steps:

```

-- Step 1

type SIGNAL TYPE is ....

-- signal's base type is SIGNAL TYPE

-- Step 2

subtype res type is res function SIGNAL TYPE;

-- name of the subtype is res_type

-- name of function is res_function

-- signal type is res_type (a subtype of SIGNAL_TYPE)

-- Step 3

function res function (DATA: ARRAY TYPE)

return SIGNAL TYPE is

-- declaration of the resolution function

-- ARRAY TYPE must be an unconstrained array of

SIGNAL_TYPE

. . .

-- Step 4

signal resolved_signal_name:res_type;

-- resolved signal name is a resolved signal

. . .

```

- 1. The signal's base type is declared.

- 2. The resolved signal's subtype is declared as a subtype of the base type and includes the name of the resolution function.

- 3. The resolution function itself is declared (and later defined).

- 4. Resolved signals are declared as resolved subtypes.

FPGA *Express* does not support arbitrary resolution functions. Only wired AND, wired OR, and three-state functions are allowed. FPGA *Express* requires that you mark all resolution functions with a special directive indicating the kind of resolution performed.

Note: FPGA Express considers the directive only when creating hardware. The body of the resolution function is parsed but ignored. Using unsupported VHDL constructs generates errors.

Do not connect signals that use different resolution functions. FPGA Express supports only one resolution function per network. The three resolution function directives are

- -- synopsys resolution\_method wired\_and

- -- synopsys resolution\_method wired\_or

- -- synopsys resolution\_method three\_state

## Note: Pre-synthesis and post-synthesis simulation results might not match if the body of the resolution function used by the simulator does not match the directive used by the synthesizer.

Example 3-17 shows how to create and use resolved signals, and how to use compiler directives for resolution functions. The signal's base type is the predefined type BIT.

```

package RES_PACK is

function RES_FUNC(DATA: in BIT_VECTOR) return BIT;

subtype RESOLVED_BIT is RES_FUNC BIT;

end;

package body RES_PACK is

function RES_FUNC(DATA: in BIT_VECTOR) return BIT

is

-- pragma resolution_method wired_and

begin

-- The code in this function is ignored by FPGA

Express

-- but parsed for correct VHDL syntax

for I in DATA' range loop

if DATA(I) = '0' then

return '0';

end if;

end loop;

return '1';

end;

end;

use work.RES_PACK.all;

entity WAND_VHDL is

port(X, Y: in BIT; Z: out RESOLVED_BIT);

end WAND_VHDL;

architecture WAND_VHDL of WAND_VHDL is

begin

Z \leq Xi

Z <= Y;

end WAND VHDL;

```

### **Variable Declarations**

Variable declarations define a named value of a given type.

You can use variables in expressions, as described in Chapter 5, "Expressions." Variables are assigned values by variable assignment statements, as described in Chapter 6, "Sequential Statements." variable A, B: BIT; variable INIT: NEW\_BIT;

Note: Variables are declared and used only in processes and subprograms, because processes and subprograms cannot declare signals for internal use.

# **Structural Design**

FPGA *Express* works with one or more designs. Each entity (and architecture) in a VHDL description is translated to a single design in FPGA *Express*. Designs can also originate from formats other than VHDL, such as equations, Programmable Logic Arrays (PLAs), state machines, other HDLs, or netlists.

A design can contain instances of lower-level designs, connected by nets (signals) to the lower-level design's ports. These lower-level designs can consist of other entities from a VHDL design, designs represented in another Synopsys format, or cells from a technology library. By instantiating designs within designs, you create a hierarchy.

Hierarchy in VHDL is specified by using component declarations and component instantiation statements. To include a design, you must specify its interface with a component declaration. You can then create an instance of that design by using the component instantiation *statement*.

If your design consists only of VHDL entities, every component declaration statement corresponds to an entity in the design. If your design uses designs or technology library cells not described in VHDL, create component declarations without corresponding entities. You can then use FPGA *Express* to associate the VHDL component with the non-VHDL design or cell.

Note: To simulate your VHDL design, you must provide entity and architecture descriptions for all component declarations.

## **Using Hardware Components**

VHDL includes constructs to use existing hardware components. These structural constructs can be used to define a netlist of components.

The following sections describe how to use components and how FPGA *Express* configures these components.

## **Component Declaration**

You must declare a component in an architecture or package before you can use (instantiate) it. A component declaration statement is similar to the entity specification statement described earlier, in that it defines the component's interface.

The syntax for a component declaration is

```

component identifier

[ generic( generic_declarations ) ]

[ port( port_declarations ) ]

end component ;

```

where identifier is the name of this type of component, and the syntax of generic\_declarations and port\_declarations is the same as defined previously for entity specifications.

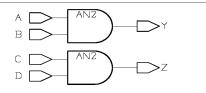

Example 3-19 shows a simple component declaration statement.

Example 3-19 Component Declaration of a Two-Input AND Gate

Example 3-20 shows a component declaration statement that uses a generic parameter.

```

component ADD

generic(N: POSITIVE);

port(X, Y: in BIT_VECTOR(N-1 downto 0);

Z: out BIT_VECTOR(N-1 downto 0);

CARRY: out BIT)

end component;

```

Although the component declaration statement is similar to the entity specification, it serves a different purpose. The component declaration is required to make the design entity AND2 or ADD usable, or visible, within an architecture. After a component is declared, it can be used in a design.

### **Sources of Components**

A declared component can come from the same VHDL source file, from a different VHDL source file, from another format such as Electronic Data Interchange Format (EDIF) or state table, or from a technology library. If the component is not in one of the current VHDL source files, it must already be compiled by FPGA *Express*.

When FPGA *Express* compiles a design that uses components, FPGA *Express* searches for previously compiled components by name in the following order:

- 1. In the current design.

- 2. In the input source file or files identified in the FPGA *Express* Implementation window.

- 3. In the libraries of technology-specific FPGA components.

### **Consistency of Component Ports**

FPGA *Express* checks for consistency among its VHDL entities. For other entities, the port names are taken from the original design description.

- For components in a technology library, the port names are the input and output pin names.

- For EDIF designs, the port names are the EDIF port names.

The bit widths of each port must also match. FPGA *Express* verifies matching for VHDL components, because the port types must be identical. For components from other sources, FPGA *Express* checks when linking the component to the VHDL description.

## **Component Instantiation Statement**

The component instantiation statement instantiates and connects components to form a netlist (structural) description of a design. A component instantiation statement can create a new level of design hierarchy.

The syntax of the component instantiation statement is

```

instance_name : component_name

[ generic_map (

generic_name => expression

{ , generic_name => expression }

) ]

port map (

[ port_name => ] expression

{ , [ port_name => ] expression }

);

```

instance\_name is the name of this instance of component type component\_name.

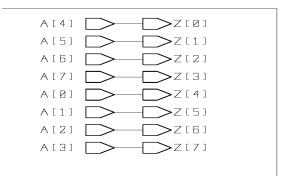

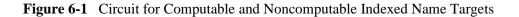

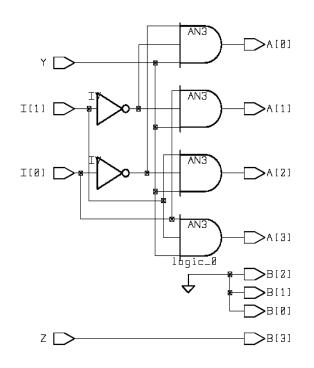

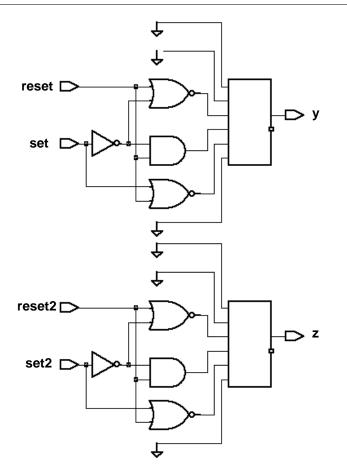

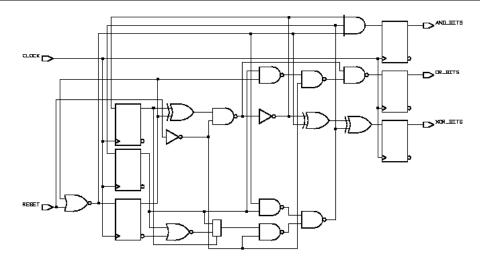

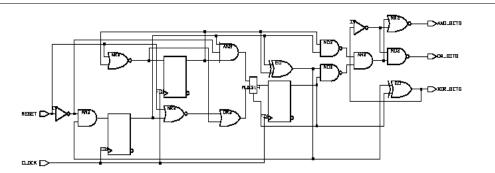

The optional generic map assigns nondefault values to generics. Each generic\_name is the name of a generic, exactly as declared in the corresponding component declaration statement. Each expression evaluates to an appropriate value.