Guide

for Synopsys simulator

Compiling the design

Compiling your design

Now lets compile yours VHDL files in correct order. Compile one design file mux.vhdl.

·

vhdlan

mux.vhd

You can compile all files at once. The first file in a line will be compiled firstly. You can compile mux.vhd and t_mux.vhd together at one time as following:

·

vhdlan

mux.vhd t_mux.vhd

If your design contains errors, you will see the message in following format:

Error: [file_name(line_number)] description….

- Correct

errors in the source file and re-compile the design

- create the simulation executable “scsim” with

scs

TB_MUX

Here, TB_MUX is the name of the configuration you wish to simulate.

Simulation

For simulation the VHDL files we would use scirocco tool in GUI mode, which is part of Synpsys.

Scirocco Tool Launch

To launch the tool type the following (you need to be in the directory where scsim file is – the result executable file of the compilation):

·

scirocco

&

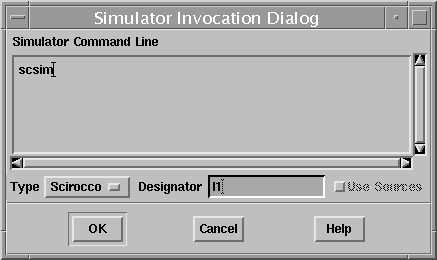

This will open Simulator Invocation Dialog Figure 1, where

· type Scirocco must be chosen for simulation the VHDL design

· click OK to launch the simulator

Figure 1 Scirocco simulator invocation dialog

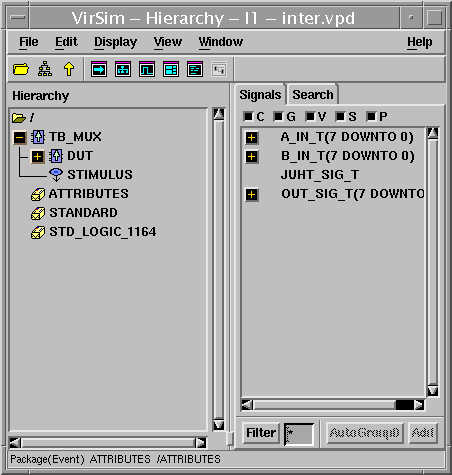

The Interactive Window with the name “VirSim-Interactive –SIM …” will open (Figure 2).

Figure 2 Interactive window of scirocco

Organizing the Display

Three important windows are Interactive Window, Hierarchy Window and the Waveform Window. You can open Hierarchy Window:

- Window

->Hierarchy

And Waveform Window:

- Window

-> Waveform

In the Interactive Window there is Command line, where you can type any command.

- Check with ls what design elements you have in this directory

Traversing the design hierarchy

In the Hierarchy window (Figure 3) you can see the hierarchy of your design and signals window will display all the signals of chosen hierarchy.

Figure 3 Hierarchy window

- Click to plus of TB_MUX in hierarchy and all the signals of this design unit will appear in signals tab.

Displaying signals in waveform window

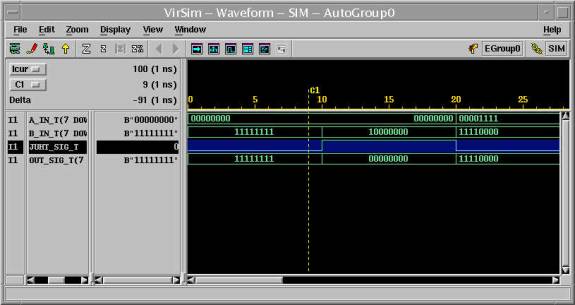

For debugging purposes, you can view signals within your design. The waveform window (Figure 4) displays the signals’ current value as well as any history.

Figure 4 Waveform window

You can add signals into the waveform window:

- Select in the signals tab of Hierarchy window signals, which you want to see on the waveform diagram (with the help of Control key) and click the button Add, which would be activated after signals choice.

Chosen signals must appear in the waveform window.

- Control if all signals appear in the list of signals of Waveform Window

Controlling the simulation

Running the simulation

You can run the simulation for a set amount of time by typing run X in the command line of Interactive window, where X is the number of nanoseconds that you wish to run for, for example run for 100 ns

- run 100 ns.

With typing just run

without specifying the time, the simulator will run for default amount of time,

which is specified in the part of Interactive window “Simulator

Control” under step time.

· Control the behavior of the design in waveform window

Using the waveform display

Observe the behaviour of the design in the waveform display. You can zoom in and zoom out the view of waveforms.

- Zoom

-> Zoom In or Zoom -> Zoom Out

- Highlight

a signal and then by mouse right button click change the display format

Restart the Simulation

The simulation can be restarted to time 0 using the restart command. When this happens, the simulator reloads any re-compiled design files the libraries. In this case, as you have just re-compiled your edited source code into the work library, the simulator will restart using your modified code.

- Click in the Interactive window to make it active

- Type restart in the command line

The simulation time will be set back to zero.

Note that the signals are still listed in the waveform display, but the previous waveforms are no longer displayed.

Quitting the simulator

When you have finished simulating, quit the simulator:

·

Type quit

in the command line of Interactive window

or

·

Sim -> Finish

Re-executing the simulation

· Sim -> Re-exec