# EEL 5722C Field-Programmable Gate Array Design

#### Lecture 17: Describing Synthesizable RTL in SystemC\*

Prof. Mingjie Lin

Stands For Opportunity

\* 2001 Synopsys, Inc. 1

# System-Level Design

- Specifying the system

- Verifying its functionality

- Determining optimum system architecture by evaluating design alternatives

Today's complex systems have significant software content and are integrated into a system on a chip (SoC).

# System-Level Design Challenges

- Component Integration

- widely implemented strategy for handling complexity, but many of the components are provided from various sources.

- Tool Interoperability

- each tool uses a proprietary model format, which makes a model developed for one tool unsuitable for use with another tool

- Design Team Collaboration

- Effective architecture design requires participation of the hardware and software design teams for creating models and influencing architectural decisions, which is called hardware-software co-design

# Why Synthesis From SystemC?

- Imagine you are a hardware designer, you are given a architectural model contains a variety of models, including processor models, abstract bus models, and peripheral models. You need to implement the peripherals and verify the implementation in the context of the entire system.

- If you use a Verilog or VHDL synthesis tool, you need to rewrite the peripheral models in Verilog or VHDL, which is a time-consuming and errorprone process

# Why Synthesis From SystemC?

- Or you can synthesize the peripheral models from SystemC

- Instead of throwing away the work done at the system level and recoding the design, you can take the abstract, non-synthesizable peripheral models and refine them into synthesizable models

- Verification Reuse

- use the system-level verification environment to check the correctness of your implementation as you refine it.

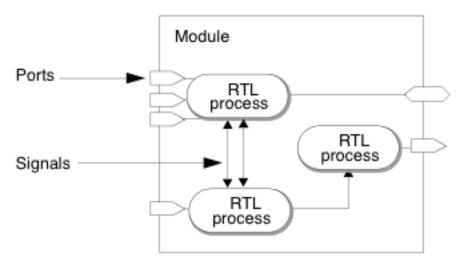

# **Defining Modules and Processes**

- The basic building block in SystemC is the module

- A SystemC module is a container in which processes and other modules are instantiated

- A typical module can have:

- Single or multiple RTL processes to specify combinational or sequential logic

- Multiple RTL modules to specify hierarchy

- One or more member functions that are called from within an instantiated process or module

6

# Module Example

- Processes

- describe the parallel behavior of hardware systems

- processes execute concurrently rather than sequentially like C++ functions

- The code within a process, however, executes sequentially

**Registering a Process**

- Triggering Execution of a Process

- Reading and Writing Processes

- Types of Processes

# **Creating a Module**

```

#include "systemc.h"

SC_MODULE (module_name) {

//Module port declarations

//Signal variable declarations

//Data variable declarations

//Member function declarations

//Method process declarations

```

};

- Coding practice

- Separate header file (module\_name.h)

- Implementation file (module\_name.cpp or module\_name.cc)

#### Module Header File

- Port declarations

- Internal signal variable declarations

- Internal data variable declarations

- Process declarations

- Member function declarations

- Module constructor

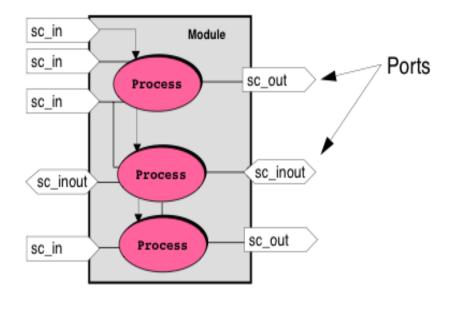

### **Module Ports**

SC\_MODULE (module\_name) {

//Module port declarations

sc\_in<port\_data\_type> port\_name;

sc\_out<port\_data\_type> port\_name;

sc\_inout<port\_data\_type> port\_name;

sc\_in<port\_data\_type> port\_name;

sc\_in<port\_data\_type> port\_name;

};

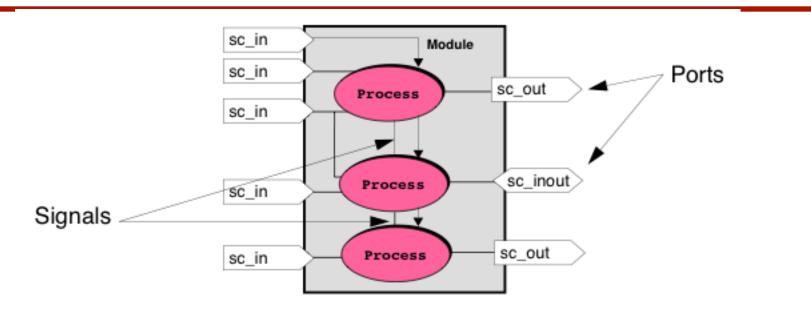

# Signals

- Modules use ports to communicate with other modules

- In hierarchical modules, use signals to communicate between the ports of instantiated modules

- internal signals for peer-to-peer communication between processes within the same module

## signal Syntax

```

SC MODULE (module name) {

//Module port declarations

sc in<port type> port name;

sc out<port type> port name;

sc in<port type>port name;

//Internal signal variable declarations

sc signal<signal type> signal name;

sc signal<signal type> signal1, signal2;

//Data variable declarations

//Process declarations

//Member function declarations

//Module constructor

SC CTOR (module name) {

//Register processes

//Declare sensitivity list

}

};

```

## **Data Member Variables**

```

SC_MODULE (module_name) {

//Module port declarations

sc_in<port_type> port_name;

sc_out<port_type> port_name;

sc_in port_name;

```

```

//Internal signal variable declarations

sc_signal<signal_type> signal_name;

```

```

//Data member variable declarations

int count_val; //Internal counter

sc_int<8> mem[1024]; //Array of sc_int

```

```

//Process declarations

//Member function declaration

```

};

Do not use data variables for peer-topeer communication in a module. This can cause pre- and postsynthesis simulation mismatches and nondeterminism (order dependency) in your design.

### Creating a Process in a Module

```

SC MODULE(my module) {

// Ports

sc in<int> a;

sc in<bool> b;

sc out<int> x;

sc out<int> y;

// Internal signals

sc signal<bool>c;

sc signal<int> d;

// process declaration

void my method proc();

// module constructor

SC CTOR(my module) {

// register process

SC_METHOD(my_method_proc);

// Define the sensitivity list

}

};

```

# **Defining the Sensitivity List**

Defining a Level-Sensitive Process

};

```

SC MODULE(my module) {

// Ports

sc in<int> a;

sc in<bool> b;

sc out<int> x;

sc out<int> y;

// Internal signals

sc signal<bool>c;

sc signal<int> d;

sc signal<int> e;

// process declaration

void my method proc();

// module constructor

SC CTOR(my module) {

// register process

SC METHOD(my method proc);

// declare level-sensitive sensitivity list

sensitive << a << c << d; // Stream declaration

sensitive(b); //Function declaration

sensitive(e); //Function declaration

}

```

# **Defining the Sensitivity List**

• Defining a Edge-Sensitive Process

```

SC MODULE(my module) {

// Ports

sc in<int> a;

sc in<bool> b;

sc in<bool> clock;

sc out<int> x;

sc out<int> y;

sc in<bool> reset;

// Internal signals

sc signal<bool>c;

sc signal<int> d;

// process declaration

void my method proc();

// module constructor

SC CTOR(my module) {

// register process

SC METHOD(my method proc);

// declare sensitivity list

sensitive_pos (clock); //Function delaration

sensitive neg << b << reset; // Stream declaration

}

```

};

# Limitations for Sensitivity Lists

- You cannot specify both edge-sensitive and level-sensitive inputs in the same process for synthesis.

- You cannot declare an sc\_logic type for the clock or other edge-sensitive inputs. You can declare only an sc\_in<bool> data type.

# Module Constructor

- Register processes

- Define a sensitivity list for an SC\_METHOD process

### Implementing the Module

```

#include "systemc.h"

#include "my_module.h"

void my_module::my_method_proc() {

// describe process functionality as C++ code

}

```

### **Reading and Writing Ports and Signals**

```

//...

// read method

address = into.read(); // get address

// assignment

temp1 = address; // save address

data_tmp = memory[address]; // get data from memory

// write method

outof.write(data_tmp); // write out

// assignment

temp2 = data_tmp; // save data_tmp

//...

```

## Reading and Writing Bits of Ports and Signals

```

//...

sc_signal <sc_int<8> > a;

sc_int<8> b;

bool c;

b = a.read();

c = b[0];

```

// c = a[0]; /Does not work in SystemC

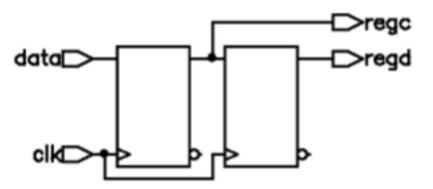

### Signal and Port Assignments

```

#include "systemc.h"

SC_MODULE(rtl_nb) {

sc_in<bool> clk;

sc_in<bool> data;

sc_inout<bool> regc, regd;

void reg_proc() {

regc.write(data.read());

regd.write(regc.read());

}

SC_CTOR(rtl_nb) {

SC_METHOD(reg_proc);

sensitive_pos << clk;

}

};</pre>

```

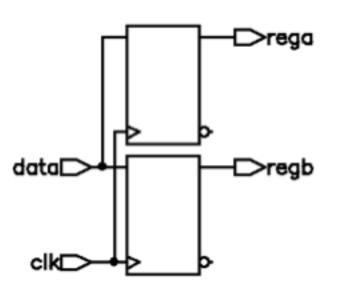

## Variable Assignment

```

#include "systemc.h"

SC_MODULE(rtl_b) {

sc in<bool> clk;

sc in<bool> data;

sc out<bool> rega, regb;

bool rega v, regb v;

void reg proc() {

rega_v = data.read();

regb_v = rega_v;

rega.write(rega_v);

regb.write(regb v);

}

SC_CTOR(rtl_b) {

SC METHOD(reg proc);

sensitive_pos << clk;

}

};

```

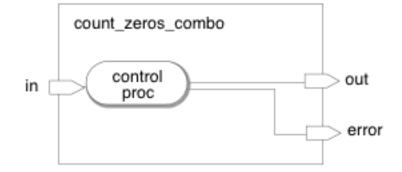

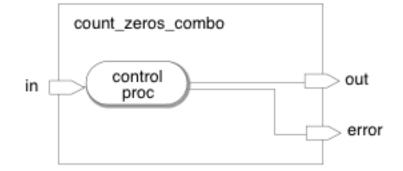

## Creating a Module With a Single SC\_METHOD Process

};

```

/****count_zeros_comb.h file***/

#include "systemc.h"

```

SC\_MODULE(count\_zeros\_comb) {

sc\_in<sc\_uint<8> > in;

sc\_out<sc\_uint<4> > out;

sc out<bool> error;

```

bool legal(sc_uint<8> x);

sc_uint<4> zeros(sc_uint<8> x);

void control_proc();

```

```

SC_CTOR(count_zeros_comb) {

SC_METHOD(control_proc);

sensitive << in;

}</pre>

```

### Creating Module With Single SC\_METHOD Process

```

/****count_zeros_comb.cpp file****/

#include "count_zeros_comb.h"

```

```

void count_zeros_comb::control_proc() {

sc_uint<4> tmp_out;

bool is_legal = legal(in.read());

error.write(! is_legal);

is_legal ? tmp_out = zeros(in.read()) : tmp_out = 0;

out.write(tmp_out);

```

```

}

```

```

bool count_zeros_comb::legal(sc_uint<8> x) {

bool is legal = 1;

bool seenZero = 0;

bool seenTrailing = 0;

for (int i=0; i <=7; ++i) {

if (seenTrailing && (x[i] == 0)) {

is legal = 0;

break;

} else if (seenZero && (x[i] == 1)) {

seenTrailing = 1;

} else if (x[i] == 0) {

seenZero = 1;

}

}

return is legal;

}

sc uint<4> count zeros comb::zeros(sc uint<8> x) {

int count = 0;

for (int i=0; i <= 7; ++i) {

if (x[i] == 0)

++count;

}

return count;

```

## **Final issues**

- Come by my office hours (right after class)

- Any questions or concerns?