## EEL 5722C Field-Programmable Gate Array Design

#### Lecture 15: Introduction to SystemC\* (cont.)

Prof. Mingjie Lin

**Stands For Opportunity**

# Starting Example:Full Adder

| FullAdder.h                                                                        | FullAdder.cpp                                                                                                                                                                              |

|------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SC_MODULE( FullAdder ) {                                                           | <pre>void FullAdder::dolt( void ) {     sc_int&lt;16&gt; tmp_A, tmp_B;     sc_int&lt;17&gt; tmp_R;     tmp_A = (sc_int&lt;16&gt;) A.read();     tmp_B = (sc_int&lt;16&gt;) B.read();</pre> |

| SC_CTOR( FullAdder ) {<br>SC_METHOD( dolt );<br>sensitive << A;<br>sensitive << B; | <pre>tmp_R = tmp_A + tmp_B; result.write( (sc_uint&lt;16&gt;) tmp_R.range(15,0) ); }</pre>                                                                                                 |

| }                                                                                  |                                                                                                                                                                                            |

};

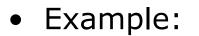

# **Modules**

#### SC\_MODULE(filter) {

// <u>Sub-modules : "components"</u>

sample \*s1;

coeff \*c1;

mult \*m1;

sc\_signal<sc\_uint 32> > q, s, c; // Signals

// Constructor : "architecture"

SC\_CTOR(filter) {

// Sub-modules instantiation and mapping s1 = new sample ("s1"); s1->din(q); // named mapping s1->dout(s);

c1 = new coeff("c1"); c1->out(c); // named mapping

m1 = new mult ("m1"); (\*m1)(s, c, q); // <u>Positional mapping</u>

}

}

- Processes are functions that are identified to the SystemC kernel. They are called if one signal of the sensitivity list changes its value.

- Processes implement the funcionality of modules

- Processes are very similar to a C++ function or method

- Processes can be Methods, Threads and CThreads

### • Methods

When activated, executes and returns

- SC\_METHOD(process\_name)

### • Threads

Can be suspended and reactivated

- wait() -> suspends

- one sensitivity list event -> activates

- SC\_THREAD(process\_name)

### • CThreads

Are activated in the clock pulse

- SC\_CTHREAD(process\_name, clock value);

| Туре                                        | SC_METHOD                                                                                                        | SC_THREAD                                                                                                        | SC_CTHREAD                                                                               |

|---------------------------------------------|------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|

| Activates Exe<br>c.                         | Event in sensit. list                                                                                            | Event in sensit. List                                                                                            | Clock pulse                                                                              |

| Suspends Exe<br>c.                          | NO                                                                                                               | YES                                                                                                              | YES                                                                                      |

| Infinite Loop                               | NO                                                                                                               | YES                                                                                                              | YES                                                                                      |

| suspended/ r<br>eactivated by               | N.D.                                                                                                             | wait()                                                                                                           | wait()<br>wait_until()                                                                   |

| Constructor &<br>Sensibility def<br>inition | <pre>SC_METHOD(call_back);     sensitive(signals);     sensitive_pos(signals);     sensitive_neg(signals);</pre> | <pre>SC_THREAD(call_back);     sensitive(signals);     sensitive_pos(signals);     sensitive_neg(signals);</pre> | SC_CTHREAD(<br>call_back,<br>clock.pos());<br>SC_CTHREAD(<br>call_back,<br>clock.neg()); |

• Process Example

Into the .H file

void doIt( void );

}

```

SC_CTOR( Mux21 ) {

```

SC\_METHOD( doIt );

sensitive << selection;

sensitive << in1;

sensitive << in2;</pre>

Into the .CPP file

```

void Mux21::doIt( void ) {

```

```

sc_uint<8> out_tmp;

```

```

if( selection.read() ) {

out_tmp = in2.read();

} else {

out_tmp = in1.read();

}

out.write( out_tmp );

```

7

# **Ports and Signals**

- Ports of a module are the external interfaces that pass information to and from a module

- In SystemC one port can be *IN*, *OUT* or *INOUT*

- Signals are used to connect module ports allowing modules to communicate

- Very similar to ports and signals in VHDL

# **Ports and Signals**

- Types of ports and signals:

- All natives C/C++ types

- All SystemC types

- User defined types

- How to declare

- IN : sc\_in<port\_typ>

- OUT : sc\_out<port\_type>

- Bi-Directional : sc\_inout<port\_type>

# **Ports and Signals**

- How to read and write a port ?

- Methods read( ); and write( );

- Examples:

- in\_tmp = in.read( ); //reads the port in to in\_tmp

- out.write(out\_temp); //writes out\_temp in the out port

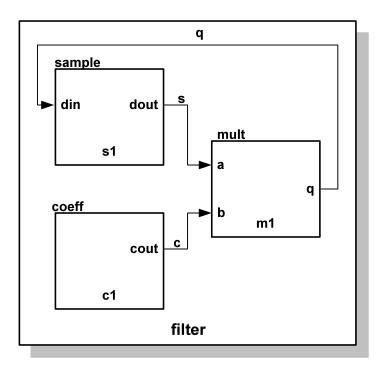

- Special object

- How to create ?

- sc\_clock *clock\_name* (

"clock\_label", period, duty\_ratio, offset, initial\_value );

- Clock connection

f1.clk( clk\_signal ); //where f1 is a

- Clock example:

# **Data Types**

- SystemC supports:

- C/C++ native types

- SystemC types

- SystemC types

- Types for systems modelling

- 2 values ('0','1')

- 4 values ('0','1','Z','X')

- Arbitrary size integer (Signed/Unsigned)

- Fixed point types

| Туре       | Description                       |

|------------|-----------------------------------|

| sc_logic   | Simple bit with 4 values(0/1/X/Z) |

| sc_int     | Signed Integer from 1-64 bits     |

| sc_uint    | Unsigned Integer from 1-64 bits   |

| sc_bigint  | Arbitrary size signed integer     |

| sc_biguint | Arbitrary size unsigned integer   |

| sc_bv      | Arbitrary size 2-values vector    |

| sc_lv      | Arbitrary size 4-values vector    |

| sc_fixed   | templated signed fixed point      |

| sc_ufixed  | templated unsigned fixed point    |

| sc_fix     | untemplated signed fixed point    |

| sc_ufix    | untemplated unsigned fixed point  |

### • Simple bit type

- Assignment similar to *char*

- $my_bit = 1';$

- Declaration

- bool my\_bit;

#### Operators

| Bitwise    | & ( <b>and)</b> | (or) | ^ (xor) | $\sim$ (not) |

|------------|-----------------|------|---------|--------------|

| Assignment | =⊅              | &=♪  | =♪      | ^=♪          |

| Equality   | ==⊅             | !=♪  |         |              |

#### • SC\_LOGIC type

- More general than *bool*, 4 values :

- (`0' (false), `1' (true), `X' (undefined) , `Z'(high-impedance) )

- Assignment like bool

- my\_logic = `0';

- my\_logic = `Z';

- Simulation time bigger than bool

- Operators like *bool*

- Declaration

- sc\_logic my\_logic;

#### • Fixed precision integers

- Used when arithmetic operations need fixed size arithmetic operands

- *INT* can be converted in *UINT* and vice-versa

- "int" in C++

- The size depends on the machine

- Faster in the simulation

- 1-64 bits integer

- sc\_int<n> -- signed integer with n-bits

- sc\_uint<n> -- unsigned integer with n-bits

#### Simple bit type

Assignment similar to char

my\_bit = `1';

Declaration

bool my\_bit;

| Operators  |                 |              |         |              |  |

|------------|-----------------|--------------|---------|--------------|--|

| Bitwise    | & ( <b>and)</b> | (or <b>)</b> | ^ (xor) | $\sim$ (not) |  |

| Assignment | =⊅              | 4&           | =♪      | ^=♪          |  |

| Equality   | ==⊅             | !=♪          |         |              |  |

#### • Arbitrary precision integers

- Integer bigger than 64 bits

- sc\_bigint<n>

- sc\_biguint<**n**>

- More precision, slow simulation

- Operators like SC\_LOGIC

- Can be used together with:

- Integer C++

- sc\_int, sc\_uint

- Bit vector

- sc\_bv<n>

- 2-value vector (0/1)

- Not used in arithmetics operations

- Faster simulation than *sc\_lv*

- Logic Vector

- sc\_lv<**n**>

- Vector to the *sc\_logic* type

- Assignment operator ("=")

- my\_vector = "XZ01"

- Conversion between vector and integer (int or uint)

- Assignment between sc\_bv and sc\_lv

- Additional Operators

| Reduction  |             | or_reduction() | xor_reduction() |

|------------|-------------|----------------|-----------------|

| Conversion | to_string() |                |                 |

Т

- Examples:

- sc\_bit y, sc\_bv<8> x;

- y = x[6];

- sc\_bv<16> x, sc\_bv<8> y;

- y = x.range(0,7);

- sc\_bv<64> databus, sc\_logic result;

- result = databus.or\_reduce();

- sc\_lv<32> bus2;

- cout << "bus = " << bus2.to\_string();</pre>

# **User defined types**

#### • Comparation operator

- Operator "Built-in" "==" can't be used

- function inline must be defined for user types

```

inline bool operator == (const packet_type& rhs) const

{♪

```

```

return (rhs.info==info && rhs.seq==seq &&

rhs.retry==retry);

```

}

# Debugging

• C++ "printf" debugging

#### printf("Hello World");

#### cout << "Hello World" << endl;</pre>

- Constructor Debugging

- Find out how your design is built up when the simulation starts.

- Use the **name()** method to identify SystemC classes:

```

SC_CTOR(nand2) {

cout << "Constructing nand2 " << name() << endl;

...

...

}

OUTPUT:

Constructing stim

Constructing nand2 exor2.N1

Constructung nand2 exor2.N2</pre>

```

- Debugging methods available on all SystemC objects:

- const char\* name()

- Returns the name of the object

- const char\* kind()

- Returns the object's sub-class name

- void print(ostream& out)

- Prints the object's name to the output stream

- void dump(ostream& out)

- Prints the objects diagnostic data to the output stream.

- Debugging threads and methods

- All SystemC data types can be "printed" to **cout**.

- e.g.: print inputs A, B, and F to **cout** in a table:

| OUTPUT : |       |

|----------|-------|

| Time     | ABF   |

| 10 ns    | 1 0 0 |

| 20 ns    | 1 1 0 |

| 30 ns    | 1 1 1 |

| 40 ns    | 0 0 1 |

```

SC MODULE (mon)

sc in<bool> A,B,F;

sc in<bool> Clk;

void monitor()

{

cout << "Time A B F" << endl;

while (true)

{

cout << sc_time_stamp() << ", ";</pre>

cout << A.read() << ", ";</pre>

cout << B.read() << ", ";</pre>

cout << F.read() << endl;</pre>

wait(); // wait for 1 clock cycle

}

SC CTOR (mon)

SC THREAD (monitor);

sensitive << Clk.pos();</pre>

```

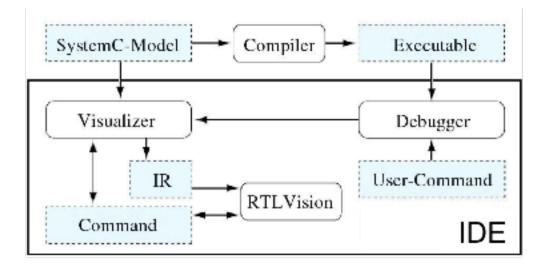

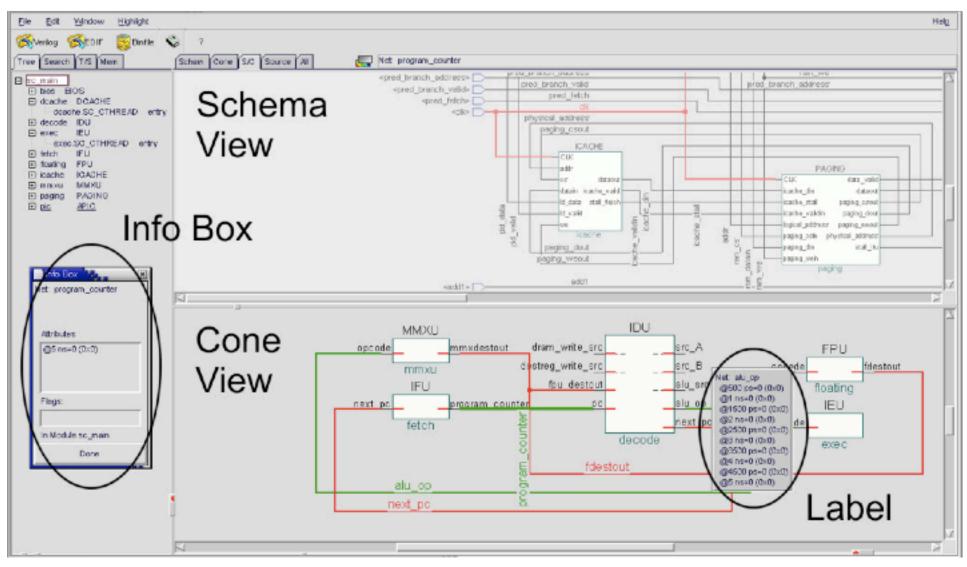

### **Advanced Debugging**

- Standard C++ debugging tools

- GDB, etc...

- SystemC-specific debuggers and visualizers.

### **Advanced Debugging**

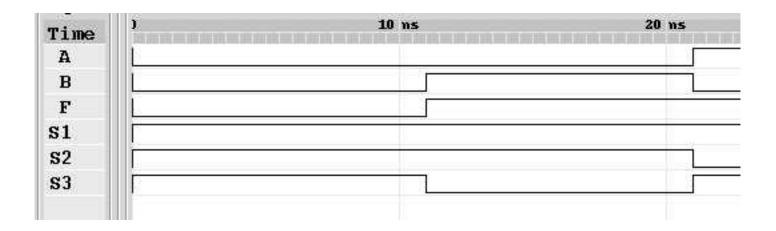

# Wave-form Debugging

- Requires adding additional SystemC statements to sc\_main()

- Wave-form data written to file as simulation runs.

- Sequence of operations:

- Declare and create the trace file

- Register signals or events for tracing

- Run the simulation

- Close the trace file

### **Wave-form Tracing**

```

int sc main(int argc, char* argv[])

sc signal<bool> ASig, BSig, FSig;

sc clock TestClk("TestClock", 10, SC NS,0.5, 1, SC NS);

// Set up simulation

. . .

// Set up trace file

sc trace file* Tf;

((vcd trace file*)Tf)->sc set vcd time unit(-9); // Set time unit

sc trace(Tf, ASig , "A" );

// Register signals

sc trace(Tf, BSig , "B" );

// and variables.

sc trace(Tf, FSig , "F" );

sc trace(Tf, DUT.S1, "S1");

sc trace(Tf, DUT.S2, "S2");

sc trace(Tf, DUT.S3, "S3");

sc start(); // run forever

// Start the simulation

sc close vcd trace file(Tf);

// Close the trace file

return 0;

```

### Wave-form Tracing

• Sample Output

### **Final issues**

- Come by my office hours (right after class)

- Any questions or concerns?